# Accelerating Hash-Based Polynomial Commitment Schemes with Linear Prover Time

Florian Hirner<sup>†</sup>, Florian Krieger<sup>†</sup>, Constantin Piber and Sujoy Sinha Roy

Institute of Information Security, Graz University of Technology, Austria firstname.lastname@tugraz.at

**Abstract.** Zero-knowledge proofs (ZKPs) are cryptographic protocols that enable one party to prove the validity of a statement without revealing any information beyond its truth. Central building blocks in many ZKPs are polynomial commitment schemes (PCS) where constructions with *linear-time provers* are especially attractive. Two such examples are Brakedown and its extension Orion, which enable linear-time and quantum-resistant proving by leveraging linear-time encodable Spielman codes. However, these PCS operate over large datasets, creating significant computational bottlenecks. For example, committing to and proving a degree 2<sup>28</sup> polynomial requires around 1.1 GB of data while taking 463 seconds on a high-end server CPU.

This work addresses the performance bottleneck in Orion-like PCS by optimizing their most critical operations: Spielman encoding and Merkle commitments. These operations involve Gigabytes of data and suffer from random off-chip memory access patterns that drastically reduce off-chip bandwidth. We resolve this issue and introduce *inverted expander graphs* to eliminate random writes and reduce off-chip memory accesses by over 50%. Additionally, we propose an on-the-fly graph sampling method that avoids streaming large auxiliary data by generating expander graphs dynamically on-chip. We also provide a formal security proof for our proposed graph transformation. Beyond encoding, we accelerate Merkle Tree construction over large data sets through a scalable multi-pass SHA3 pipeline. Finally, we reutilize existing hardware components used in commitment to accelerate the so-called proximity and consistency checks during proof generation.

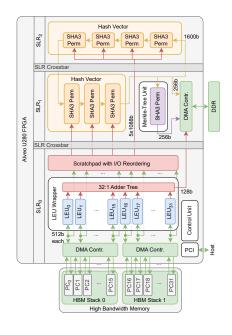

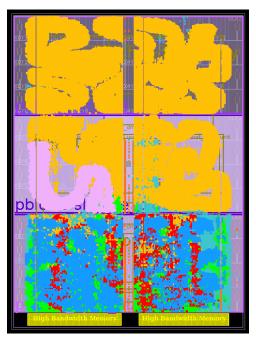

Building upon these concepts, we present the first hardware architecture for PCS—with linear prover time—on an Xilinx Alveo U280 FPGA. In addition, we discuss the practical challenges of manually partitioning, placing, and routing our large-scale architecture to efficiently map it to the multi-SLR and HBM-equipped FPGA. The final implementation achieves a speedup of two orders of magnitude for full proof generation, covering commitment and proving steps. When combined with Virgo as an outer CP-SNARK protocol, our accelerator reduces end-to-end latency by up to  $3.85\times$ —close to the theoretical maximum of  $3.9\times$ .

Keywords: Zero-Knowledge Proof  $\cdot$  Orion  $\cdot$  Brakedown  $\cdot$  Spielman Code  $\cdot$  FPGA

## 1 Introduction

Zero-knowledge proofs (ZKP) enable one party, known as the *prover*, to demonstrate to another party, known as the *verifier*, that a given statement is true without revealing any information about why the statement is true or any private data that was used to prove it. As an illustration, the prover can convince the verifier that it knows a private witness w for a public input x such that C(x, w) = 0 is satisfied for a circuit C, all without revealing any

<sup>&</sup>lt;sup>†</sup>These authors contributed equally to this work.

information about w. The concept of ZKP systems was first introduced by Goldwasser, Micali, and Rackoff in the 1980s in their seminal paper [GMR85].

ZKPs have seen growing use in recent years, with their real-life applications expected to expand further. One notable application area is verifiable computation, where a client delegates computation to a powerful but untrusted server. Subsequently, the client can easily verify (without re-doing the computation) whether the server executed the computation correctly or not. Concrete realizations of verifiable machine learning using ZKP are presented in [LXZ21, WYX<sup>+</sup>21]. ZKPs are extensively used in blockchains and cryptocurrencies to achieve anonymity and privacy [BSCG<sup>+</sup>14]. Cryptocurrency transactions can be fully encrypted on the blockchain, yet their legitimacy can still be verified using ZKP [Fou, Pro]. Other application areas include online auction [GY18], verifiable database query [LWX<sup>+</sup>23], and classical authentication systems. Recently proposed zero-knowledge proof of training framework (zkPoT) [APPK24] enables a prover to prove the correct training of a deep neuronal network on a committed dataset without disclosing any details about the model or dataset. The prover trains the model iteratively, committing to the model parameters and providing a zkPoT at each step.

Driven by the rapid development of ZKP applications, many new schemes have been recently proposed [XZS22, GLS<sup>+</sup>23, CBBZ23, DP23]. One very promising direction of scheme development involves polynomial commitment schemes (PCS) with linear prover time. In such schemes, the prover can prove to the verifier that a committed polynomial was genuinely evaluated. In addition, the prover benefits from an asymptotically linear runtime concerning the huge polynomials at hand. Usually, the polynomials have between Millions and Billions of coefficients thus necessitating an efficient prover. Brakedown [GLS+23] and its extension work Orion [XZS22] are highly interesting PCS with linear-time commitment and proving. Their cryptographic security is based on the preimage resistance of a cryptographic hash function, making them post-quantum secure and avoiding trusted setups. The fast prover and post-quantum security set Orion and Brakedown apart from commonly used proof systems [KZG10, Gro16, WTS+18, BBB+18, Lee21], which are based on pairings or discrete logarithm assumptions. The advantages of Orion and Brakedown attract broad research, mostly focusing on their cryptographic and protocol-level properties. Recent works [dHS24] improve the soundness guarantees of the Orion scheme and present the closely related Scorpius scheme. Other efforts [CBBZ23] propose new schemes re-using the linear-time encoding initially proposed in Brakedown. This underlines the relevance of Orion and Brakedown-like schemes as a polynomial commitment scheme in contemporary research. In our paper, we take Orion as a case study for post-quantum secure linearprover-time PCS due to Orion's small proof size. However, our concepts and contributions directly apply to Brakedown and other related works as well.

Motivation for hardware acceleration of Orion [XZS22]: Several works in the literature have accelerated pairing and discrete logarithm-based proof systems. However, hardware accelerating Orion (which was proposed in 2022) using FPGAs has not gained broad attention. Although Orion's commitment and proving mechanisms have linear asymptotic complexity, reaching concrete efficiency and practical performance is hard. This is due to the Gigabytes of data involved in the prover's complex computations, which reflects in low software performance [Su]. At the same time, Orion as a PCS is repeatedly used as a building block in larger ZKP applications (e.g., zkPoT [APPK24]). Hence, the commitment and proving steps of Orion are invoked multiple times within a single execution of the ZKP application. These frequent invocations require performant polynomial commitment and proving mechanisms.

A detailed timing analysis of Orion's software implementation [Su] (presented in Section 3.3) shows that the most demanding part of Orion is the polynomial commitment phase, involving linear error-correcting Spielman codes and large expander graphs. The

Spielman encoding operates over Gigabytes of data, necessitating off-chip memory storage. Even more critically, Spielman codes access the data in off-chip memory in a non-optimal random pattern, which degrades the memory bandwidth. This challenge was also identified by prior work [SLDS24], but no solution has been presented so far. Furthermore, the handling of large expander graphs within the encoding is challenging. In typical implementations, these graphs require considerable storage of several hundred Megabytes or even Gigabytes. Hence, the high demand for off-chip memory is a critical aspect of Orion and requires a memory-aware hardware design.

Another challenge in Orion's commitment is the generation of Merkle Trees. Constructing these trees quickly demands massive hashing throughput. In addition to the commitment step, the proving mechanism in Orion's software is also slow. Proving contains so-called proximity and consistency checks which compute random linear combinations of the large Spielman codewords. Subsequently, Orion Merkle-commits to the linear combinations causing a total latency of up to several seconds.

Given the performance bottlenecks in Orion, there is a strong need to explore optimization strategies that can accelerate the scheme. This paper addresses the three key operations within commitment and proving for optimization: (1) improving the performance of linear Spielman encoding by lowering the costly random off-chip memory accesses and by on-the-fly expander graph sampling, (2) optimizing the generation of Merkle Trees for faster commitment and proving in Orion, (3) accelerating the proximity and consistency checks within proving. By focusing on these core aspects, we significantly reduce the latency of the Orion PCS. Therefore, our methodology enhances the scalability and practicality of linear-prover-time PCS – such as Orion or Brakedown – for real-world applications.

#### 1.1 Contributions

We present a series of novel memory-aware optimizations to enhance the performance of Orion and Orion-like PCS. Our contributions are:

- Reduced off-chip memory accesses in Spielman encoding: We propose inverted expander graphs which relax the critical demand on off-chip memory bandwidth during linear encoding. Compared to regular expander graphs, inverted expanders save roughly 50% of off-chip memory accesses, which allows a significant improvement of computational performance. Moreover, problematic random writes are avoided entirely, and overheads due to read-write-turnarounds are reduced.

- On-the-fly graph sampling: The baseline version of both regular and inverted expander graphs requires storing the graph structure. In case of  $N=2^{28}$ , the graph structure consumes up to 1.1 Gigabytes in off-chip memory. The overall overhead is even higher when storing the graph structure of multiple N, i.e., a range of  $N=2^{16}$  to  $2^{28}$ . Loading this large data would degrade the effective off-chip bandwidth during linear encoding. We hence present an on-the-fly graph sampling method and a novel postprocessing technique that avoids off-chip storage of the graph structure. In addition, we extend Brakedown's proof [GLS+21] to show that our on-the-fly sampled inverted expander graphs do not compromise code distance.

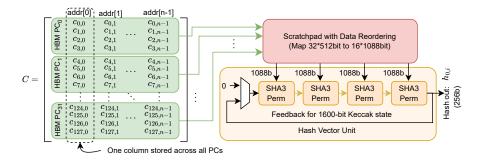

- Efficient Merkle Tree generation: We develop a pipelined method for data rearrangement and constructing Merkle Trees, which schedules interleaved hashing and Merkle Tree construction. This accelerates the computational overhead in the commitment and proving phases.

- Accelerated proximity and consistency checks: We accelerate the proximity

and consistency checks within proving by reutilizing the linear encoding datapath.

In addition, proving requires dedicated Merkle commitments, which we compute by

reusing the Merkle Tree unit. Hence, the proving step in Orion leverages existing

- hardware components to lower the latency of the overall scheme.

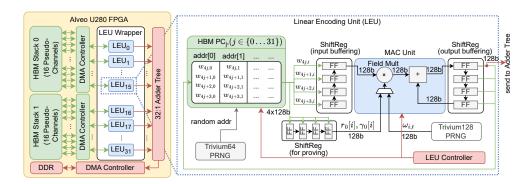

- FPGA implementation for Orion: We present the first FPGA architecture for the Orion PCS. Our heterogeneous design relies on High-Bandwidth-Memory (HBM) on an Alveo U280 datacenter FPGA [Xil19] and benefits from our memory-aware design strategy. In addition, we detail our architecture partitioning to address the physical placement challenges for the multi-SLR FPGA. Our large-scale FPGA design accelerates Orion's commitment and the proving phase by up to 264× and 65× respectively.

# 1.2 Organization

The remainder of the paper is structured as follows: In Section 2, we provide an overview of the necessary background, including expander graphs, Spielman codes, Merkle Tree commitments, and off-chip memory details. Section 3 contains a comprehensive study of proof systems, functional commitments, and the Orion scheme. In addition, we show the similarities and differences between Orion and Brakedown. Section 4 delves into the specific challenges and our proposed solutions for efficient Spielman encodings. In Section 5, we discuss the challenges associated with Merkle Tree generation and our optimized hardware-friendly approach. Section 6 presents our overall FPGA architecture and our implementation results. Section 7 compares our results to the Orion software. Section 8 discusses the impact of this work and how other PCSs can benefit from our design. Finally, Section 9 concludes the paper.

# 2 Basic Background

This section offers the essential background required to understand the contributions of this paper. To ensure the paper is self-contained, the background section is relatively extensive. For a more detailed explanation of Orion, including proofs and protocols, refer to the original Orion paper [XZS22].

#### 2.1 Notation and Acronyms

Natural numbers and field elements are denoted using lowercase letters, e.g., d. Vectors are represented by  $\vec{v}$ , while matrices are indicated by bold capital letters, such as  $\mathbf{M}$ . The element from the i-th row and j-th column is  $\mathbf{M}[i,j]$ , and the i-th column vector is  $\mathbf{M}[:,i]$ . To denote the size of a set S, we use the notation |S|. The implementation of Orion uses an extension field  $\mathbb{F}_{p^2}$ , e.g.,  $GF((2^{61}-1)^2)$  in the software developed by the authors [XZS22]. The elements of this extension field can be represented as a degree-1 polynomial a+bz where a and b are from the base field  $\mathbb{F}_p$ . It is not always necessary to use an extension field if the base field is sufficiently large. We define the Hamming weight function  $HW(\vec{v})$  to be the number of non-zero elements in the vector  $\vec{v}$ , i.e.  $HW(\vec{v}) = ||\vec{v}||_0$ . We use poly(x) to refer to a function upper-bounded by a polynomial in variable x with a constant degree. We use the base-2 logarithm unless otherwise specified.

## 2.2 Graphs and expanders

Graphs in discrete mathematics are networks of points. Formally, a graph is a set of vertices and edges, where each edge is an unordered pair of vertices representing a connection. We denote this as G = (V, E) with V as the vertex set and E as the edge set. Both sets are usually finite, though not necessarily always [Big02]. The *degree* of a vertex is the number of edges connected to it [Hei03].

- (a) General expander structure.

- (b) Example expander with expansion property highlighted.

Figure 1: Unbalanced bipartite expanders.

#### 2.2.1 Expander graphs

In an expander graph, any small subset of vertices has a large proportion of its vertices connected to vertices outside the subset [SS94], i.e., the subset 'expands' to neighbors. Formally, a graph G=(V,E) satisfies the expansion property if, for some constants  $\delta>0$  and m>0, we have:

$$\forall S \subset V, |S| \le m \Rightarrow |\{y \in V \setminus S : \exists x \in S \text{ such that } (x, y) \in E\}| \ge \delta|S| \tag{1}$$

This means that for any subset S of at most m vertices, the number of distinct vertices outside S that are connected to at least one vertex in S is at least a  $\delta$ -fraction of the size of S [Spi96]. Thus, the number of neighboring vertices grows proportionally with the size of the subset.

Bipartite expanders: The Orion proof system uses expander graphs that are also bipartite. In a bipartite graph, the set of vertices can be divided into two disjoint sets L and R such that there are no connections within L nor R. Thus, a vertex in L can only be connected to vertices in R and vice versa. We call L the left vertex set and R the right vertex set. We call such a bipartite graph G = (L, R, E) as (c, d)-regular if all vertices in L have the degree L0 and all vertices in L1 have the degree L2 and all vertices in L3 have the degree L4.

Given parameters  $\varepsilon$ ,  $\delta$  with  $0 \le \varepsilon < 1$  and  $\delta > 0$ , a (c,d)-regular graph is a  $(c,d,\varepsilon,\delta)$ -expander if it upholds the expansion property mentioned in Equation 1 for an  $\varepsilon$ -fraction of the larger vertex set L or R. In Orion, we have |L| > |R|, thus we substitute V by L in Equation 1 and set  $m = \varepsilon |L|$ . The expansion property now tells us that for every subset of left vertices, there must be outgoing connections to R depending on  $\delta$ . Figure 1a illustrates such an expander. It connects a left vertex set of  $L = \{l_1, \ldots, l_k\}$  to a right-vertex set  $R = \{r_1, \ldots, r_n\}$  with dense connections. In Figure 1b, an example is given with the expansion of vertices  $\{l_2, l_3\}$  highlighted with c = 2 and d = 3.

#### 2.2.2 Random Expanders

Constructing expander graphs is typically challenging. However, using a random construction, where edges are randomly placed between vertices, can yield good results with relatively low complexity [Spi96]. Thus, using randomized edges is a convenient way to construct a bipartite expander. Let L be the left vertex set and R be the right. Then, we can construct the edge set as follows. Set  $E_i = \{(l_i, r_t) : r_t \text{ random vertex } \in R\}$  with  $|E_i| = c$  for each vertex  $l_i \in L$ . That is, for vertex  $l_i$  of L, find c distinct random vertices in R to connect to. Then, the union  $E = \bigcup_i E_i$  of all random edge sets allows us to

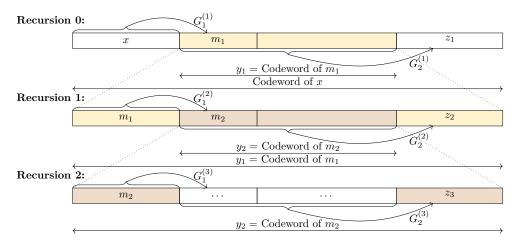

Figure 2: Illustration of the recursive Spielman encoding.

construct  $G = (L \cup R, E)$ . The chosen edges result in c neighbors for all vertices in L [Spi96] while the edges on R will follow a *binomial* distribution. Algorithm 2 shows the graph generation.

It is often desirable to prove that a particular graph G is a good expander. An efficient test for a good expander is provided in [XZS22]. They prove that a random construction as described above gives a good expander with probability  $1 - O\left(\frac{1}{\text{poly}(k)}\right)$ , where k = |L|. They define the *Very Small Set Expansion* problem distinguishing two cases [XZS22]:

- 1. Non-expanding:  $\exists S \subset L$  with  $|S| \leq \log \log k$  and Equation 1 does not hold for S.

- 2. Expanding:  $\forall S \subset L \text{ with } |S| \leq \log \log k$ , Equation 1 holds.

To test for the non-expanding case, the authors introduce an algorithm given in Algorithm 3. If this algorithm outputs NotFound, then with overwhelming probability, the graph is a good expander.

## 2.3 Spielman Codes: Linear-Time Encodable Error-Correcting Codes

The goal of an error-correcting code is to detect and correct errors, e.g., transmission errors due to the unreliability of networks [HP10]. A code is defined over an alphabet, commonly consisting of binary digits. A message with length k is encoded into a codeword, which is represented using exactly n digits of the alphabet. Of the n digits, k digits are associated with the information, while the remaining m=n-k digits are used for error detection and correction. Such a code is referred to as an [n,k,d] code, with distance d. Therein, the distance d of the code is the minimal Hamming distance between any two valid codewords. The relative distance of a [n,k,d] code is defined as  $\delta=d/n$  and the rate is  $\frac{1}{r}$  with r=n/k, which is the ratio of digits used by the code against the minimum number of digits necessary to contain the same information.

Linear codes are the most studied form of error-correcting codes. Their characteristic is that any linear combination of codewords is again a valid codeword [RL09]. The work in [Spi96] proposes the Spielman code, a linear error-reduction code with a *linear-time encoding* using expander graphs. Orion [XZS22], Brakedown [GLS<sup>+</sup>23], and related schemes use this linear-time encoding to achieve a linear-time polynomial commitment scheme. We hence explain the generalization of Spielman codes, which work over finite fields.

The construction of a linear Spielman code, denoted as  $E_C$ , for a message x uses a recursive encoding, as shown in Figure 2. The recursion step or level is indicated in superscript. At every level, two types of expander graphs,  $G_1$  and  $G_2$ , are used. In the first

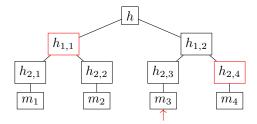

Figure 3: Merkle Tree example with l=2. Hash values for opening  $m_3$  are marked in red.

step, the k-field-element-wide message x is encoded by the expander  $G_1^{(1)} = (L_1^{(1)}, R_1^{(1)}, E_1^{(1)})$  with  $|L_1^{(1)}| = k$  and  $|R_1^{(1)}| = \alpha_1 k$ . Therein,  $\alpha_1 = \alpha$  where  $0 < \alpha < 1$  is a Spielman codespecific parameter. This encoding results in  $m_1$  with  $\alpha_1 k$  elements. Then, this procedure is applied recursively to encode  $m_1$ , as shown in Figure 2. As soon as the recursion computes the codeword for  $m_1$  and returns to level-1, a different expander  $G_2^{(1)} = (L_2^{(1)}, R_2^{(1)}, E_2^{(1)})$  is applied to the codeword of  $m_1$  which results in the final  $z_1$  component of the codeword of x. For  $G_2^{(1)}$  we have  $|R_2^{(1)}| = \alpha_2 |L_2^{(1)}|$  with  $\alpha_2 = \frac{r-1-\alpha r}{\alpha r}$ . The final Spielman codeword of x is the concatenation of x, the codeword of  $m_1$ , and  $m_1$ , as shown at the top (recursion 0) of Figure 2.

All expanders  $G_1^{(i)}$  and  $G_2^{(i)}$  for recursion i use the constant parameter  $\alpha_1$  and  $\alpha_2$ , respectively. Since  $\alpha_1 < 1$ , the encodings  $m_i$  shrink in size during the recursions, and at some point  $m_i$  will have fewer than  $n_0$  elements left, where  $n_0$  is a scheme-specific threshold for returning from the recursion. Once this threshold is reached, no further recursion occurs, and the codeword is formed by appending the input message with the result of  $G_2^{(1)}$ , as in Figure 2. The expanders used in Orion or Brakedown are public information and can be randomly generated as discussed in Section 2.2.2.

The actual evaluation of an expander graph G=(L,R,E) with |L|=k and  $|R|=\alpha_j k$  over a k-element wide message can be expressed as matrix-vector multiplication. For that, the  $k \times \alpha_j k$  adjacency matrix  $\mathbf{A}$  of the graph G is used. This matrix has  $\mathbf{A}[i][t]=0$  if there is no edge connecting node  $l_i$  in L and node  $r_t$  in R. Conversely, if  $\mathbf{A}[i][t]=\omega_{i,t}\neq 0$ , there is such an edge, and a random weight  $\omega_{i,t}$  is assigned to the edge. Based on that, the graph evaluation result m and the message x are interpreted as row vectors  $\vec{m}$  and  $\vec{x}$ , whereby  $\vec{m}=\vec{x}\mathbf{A}$ .

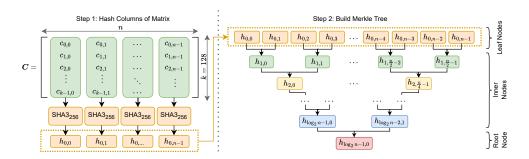

#### 2.4 Merkle Trees

A Merkle Tree is a binary tree, used to commit to a vector of  $2^l$  messages [Gol01] efficiently using a single hash value h at the root of the tree. The  $2^l$  leaf nodes store the cryptographic hashes of the  $2^l$  messages. Each non-leaf node stores the hash of its two child nodes. The root of the tree, h, serves as the final commitment, known as the Merkle commitment.

To prove the inclusion of any individual message  $m_i$  in the committed message vector, a Merkle proof  $\pi_i$  is generated. This proof consists of l hash values in a path to the root: starting from the leaf hash $(m_i)$  and the sibling node's hash at each level of the tree, all the way up to the root. A verifier combines these sibling hashes to recompute the root hash and accepts  $\pi_i$  if and only if the re-computed root hash is h. The proof generation does not reveal any other messages  $m_i \forall j \neq i$ .

Figure 3 shows a representation of the Merkle Tree for a vector of four messages  $[m_1, \ldots, m_4]$ . To prove that  $m_3$  is part of the committed vector, the prover provides the verifier with the siblings that appear in the path to the root, i.e.,  $\pi_3 = \{h_{2,4}, h_{1,1}\}$ . The verifier re-computes  $h_{2,3}$  from  $m_3$ , then  $h_{1,2}$  from  $h_{2,3}$  and  $h_{2,4}$ , and finally the root-hash from  $h_{1,1}$  and  $h_{1,2}$ . If the prover tries to cheat by claiming that a different  $m'_3$  is present

in the committed vector, then the recomputed hash will not match with the commitment h with very high cryptographic probability. This proof size is logarithmic in the number of elements in the committed vector. Such logarithmic efficiency is particularly important for cryptographic proof systems.

## 2.5 Impact of Memory Access Patterns on Off-Chip Bandwidth

In data-intensive applications, accelerators need to rely on off-chip memory like DDR4 or High Bandwidth Memory (HBM), as on-chip storage capacity is limited. The latest generation DDR or HBM may offer a high peak bandwidth, e.g., HBM2 offering up to 460 GB/s; however, such peak performance is rarely achieved in practice, particularly when memory access patterns are irregular or random. This subsection highlights how memory access patterns critically impact the effective off-chip bandwidth in data-intensive hardware accelerators, motivating the need for access-efficient designs. Communication with off-chip memory typically follows the AXI4 (Advanced eXtensible Interface) protocol [FPG], which supports two primary modes: burst and random accesses. Burst mode transfers multiple contiguous memory words in a single transaction, reducing protocol overhead and enabling memory controllers to exploit row buffering and bank-level parallelism. This allows burst transactions to utilize up to 80–95% of the theoretical bandwidth. In contrast, random accesses involve scattered, non-contiguous memory locations. These require frequent row activations and pre-charges (in DDR4) or underutilized bank parallelism (in HBM), significantly degrading performance. Random accesses are often limited to just 20-40% of the peak bandwidth, even with AXI's decoupled channel design that separates address and data phases. Empirical results from Xilinx [Xil24] on the Alveo U280 FPGA provide quantitative insights. Each HBM channel offers a theoretical 14.4GB/s bandwidth. For read operations, burst accesses achieved 13.9GB/s (96.6% utilization), while random reads dropped to 4.3GB/s (29.9%). Similarly, linear writes reached 12.9GB/s (89.7%), but random writes fell to 4.6GB/s (32.0%). Across 32 HBM channels, the aggregate practical bandwidth under random access reaches only 137.6 – 147.2GB/s, far below the 460 GB/s theoretical peak. Hence, the design methodology needs to take care of memory access patterns and optimize them to achieve high compute acceleration.

Further performance implications: The AXI4 protocol is the de facto standard for memory communication in modern FPGA- and ASIC-based accelerators. It defines independent read and write channels, each of which is further divided into address and data phases. This decoupled design allows the memory controller to issue address requests far in advance and pipeline multiple outstanding memory accesses. However, this flexibility comes at a cost. Due to the deep pipelining of off-chip memory controllers, there is often a significant initial latency between issuing an address and receiving the corresponding data. This startup latency is especially pronounced when random accesses break the streaming pattern and prevent effective prefetching or pipelining. For example, issuing a burst read may still take tens of cycles before the first data word is returned, depending on memory controller arbitration and row activation delays. Furthermore, read and write channels are not truly independent at the memory controller level. When an accelerator interleaves reads and writes, the memory controller must drain and flush internal buffers, reconfigure internal paths, and stall ongoing transfers. This results in read/write turnaround penalties, which introduce idle cycles even if the AXI interface is otherwise fully utilized. These turnarounds are particularly harmful in scenarios like Orion's expander graph evaluations, which exhibit frequent switches between read and write phases due to multiply-accumulate steps.

# 3 Background on Proof Systems

Proof systems are protocols that allow a prover to convince a verifier of the correctness of a statement. For example, the prover can demonstrate knowledge of a private witness w for a public input x such that a circuit C(x, w) = 0 holds, without disclosing w. With this hiding feature, the proof system is called 'zero-knowledge'.

Proof systems are commonly used to ensure the correctness of computations outsourced to untrusted entities. The verifier can verify the proof using a small amount of computation, hence efficiently, without performing the outsourced computation themselves. There are several important performance metrics for proof systems, such as proof generation time, proof size, and proof verification time. Usually, proof systems are optimized for succinct proofs and low verification costs. Having a low proof generation time is a plus and desired in applications that require scalability.

Modern succinct non-interactive proof systems are built by combining an interactive oracle proof (IOP) with a functional commitment scheme to form a succinct *interactive* argument. To render the proof system non-interactive, the Fiat-Shamir transform [FS86] can be used. In the following part, we describe functional commitment with a focus on the specific type of 'polynomial commitment'.

# 3.1 Functional Commitment (with a focus on polynomial commitment)

A functional commitment scheme is a commitment scheme that enables a party to commit to a function (computation procedure) they intend to evaluate. A prover can prove statements about the committed function, e.g., the evaluation of the function at a given point is correct. Functional commitment schemes have binding and optionally hiding properties. The binding property ensures that the committer cannot change the function or the input to the function, so that the commitment remains unaffected. The hiding property, which is required for zero-knowledge succinct non-interactive argument of knowledge or SNARK construction, ensures that no information about the function or the inputs to the function is revealed. A functional commitment scheme is a cryptographic protocol with an underlying cryptographic assumption, e.g., discrete logarithm assumption, pairing assumption, cryptographic hash assumption, etc.

The Merkle Tree presented in the previous subsection is a vector commitment scheme to prove membership in a committed vector. While vector commitments like Merkle Trees are useful for committing to a static set of values and proving membership, they lack the flexibility, efficiency, and built-in polynomial structure needed for polynomial-related operations. Polynomial commitments [KZG10] are functional commitments, specifically designed to address these limitations by enabling succinct proofs of evaluations, degree checks, and functional properties of polynomials, making them essential in many cryptographic applications. With a polynomial commitment scheme, a prover can commit to a polynomial, for example,  $\phi(x) \in \mathbb{F}[x]$  of degree t with coefficients from the field  $\mathbb{F}$ . Simply committing to each coefficient  $(\phi_0 || \dots || \phi_t)$  of the polynomial is ineffective, as verifying the commitment would require revealing the entire polynomial. Furthermore, many cryptographic applications require that only evaluations of  $\phi(x)$  at specific x are revealed without revealing the entire polynomial. Polynomial commitments play a crucial role in modern proof systems, e.g., SNARKs.

A polynomial commitment scheme [KZG10] consists of four main steps. First, the 'Setup Phase' involves the generation of public parameters using the SETUP algorithm for a given function family, say  $\mathcal{F}$ . In the second step, the 'Commitment Phase', the prover P uses the COMMIT algorithm and the public parameters to generate a commitment  $com_{\phi}$  for a polynomial  $\phi \in \mathcal{F}$ . Third, during the 'Evaluation Phase', the verifier V selects an evaluation point x=a and requests the prover to evaluate  $\phi$  at that point. The prover computes the value  $b=\phi(a)$  and generates an evaluation proof  $\pi$  that asserts the

correctness of this evaluation. Finally, in the 'Verification Phase', the verifier checks the validity of the proof  $\pi$  against the commitment  $com_{\phi}$ , the evaluation point a, and the claimed output b, accepting or rejecting the claim based on the result.

**Example of polynomial commitment:** To explain how a polynomial commitment scheme works, we use the famous KZG scheme [KZG10] with some simplifications. Let  $\phi(x) = \phi_0 + \phi_1 x + \dots + \phi_t x^t$  be a polynomial over  $\mathbb{Z}_p$  of degree t. The scheme uses the discrete logarithm and bilinear pairing cryptographic assumptions and requires a trusted setup. The setup generates public parameters  $PP = (g, g^s, g^{s^2}, \dots, g^{s^t}, g_2, g_2^s)$  where  $g \in G_1$  and  $g_2 \in G_2$  are generators of two bilinear groups of prime order p, and s is a secret 'toxic waste' destroyed after the setup. The bilinear pairing  $e: G_1 \times G_2 \to G_T$  is used for verification. To commit to  $\phi(x)$ , the prover computes  $com_{\phi} = g^{\phi(s)} = \prod_{i=0}^t (g^{s^i})^{\phi_i}$  which is an element of  $G_1$ . To prove that the evaluation  $y_a = \phi(x_a)$  at  $x = x_a$  is correct, the prover computes the quotient polynomial  $q(x) = \frac{\phi(x) - y_a}{x - x_a}$  and then the proof  $\pi = g^{q(s)} \in G_1$ . The verifier checks the evaluation proof  $\pi$  by using the bilinear pairing  $e(com_{\phi}/g^{y_a}, g_2) \stackrel{?}{=} e(\pi, g_2^{s-x_a})$  where  $g_2^{s-x_a}$  is precomputed from the public parameters.

The prover in the KZG polynomial commitment scheme is very slow, and due to the use of elliptic curve cryptography, the scheme is not quantum-resilient. Furthermore, the scheme requires a trusted setup. In the following, we present the basics of Orion [XZS22], which provides fast proving times, quantum resilience, and transparent setup.

# 3.2 Orion and Brakedown Proof Systems

Orion [XZS22] is a highly efficient zero-knowledge proof system that extends the Brakedown proof system [GLS+23]. Both Orion and Brakedown utilize linear-time polynomial commitments and Merkle Trees to achieve succinct proofs with fast proving. Unlike most contemporary systems with superlinear prover times [KZG10, Gro16, CHM+20], Orion's and Brakedown's provers run in linear time. Proving only relies on hash functions, making it resistant to quantum attacks, which is not the case in schemes based on discrete logarithm or pairing assumptions. Built on linear codes via expander graphs, Orion uses code-switching to achieve poly-logarithmic proof sizes. In contrast, Brakedown has a square-root proof size, leading to larger proofs. Nevertheless, Brakedown's encoding and parts of the proving mechanism are very similar to Orion, which allows extending our presented concepts to Brakedown as well. The following section explains the protocol with a focus on Orion and highlights the similarities and differences to Brakedown.

Orion and Brakedown operate on multilinear polynomials  $\phi$  in  $\log N$  variables, where each variable has a degree 0 or 1. There are N monomials and coefficients in  $\phi$ . The coefficients of  $\phi$  are in a field, say  $\mathbb{F}_{p^2}$ , and any evaluation of  $\phi$  is also performed in  $\mathbb{F}_{p^2}$ . Authors in [GLS<sup>+</sup>23] found that such a polynomial evaluation can be expressed as a tensor product. The evaluation of  $\phi$  at  $\vec{x} = [x_0, \ldots, x_{\log N-1}]$  can be written as

$$\phi(\vec{x}) = \sum_{i_0=0}^{1} \dots \sum_{i_{\log N-1}=0}^{1} w_{i_0,\dots,i_{\log N-1}} x_0^{i_0} x_1^{i_1} \dots x_{\log N-1}^{i_{\log N-1}}$$

(2)

In the above expression,  $i_0,\ldots,i_{\log N-1}$  represent the binary decomposition of monomial index  $i\in\{0,1,\ldots,N-1\}$ , and the  $w_i$  terms correspond to the coefficients of the monomials  $X_i=x_0^{i_0}x_1^{i_1}\ldots x_{\log N-1}^{i_{\log N-1}}$ . Let  $\vec{w}$  denote the vector of monomial coefficients with the i-th element  $\vec{w}[i]=w_{i_0,\ldots,i_{\log N-1}}$ . Assuming N has an integer square root (e.g., N a power of 2), let  $k=\sqrt{N}$ . Also, let  $\vec{r}_0=(X_0,X_1,\ldots,X_{k-1})$  and  $\vec{r}_1=(X_{0\cdot k},X_{1\cdot k},\ldots,X_{(k-1)\cdot k})$  be two vectors containing k distinct monomials. Then all the monomials in Equation 2 are obtained using the tensor product  $\vec{r}_0\otimes\vec{r}_1$ . Finally, the evaluation of  $\phi$  can be obtained using the inner product  $[\mathrm{GLS}^+23]$  as  $\phi(x_0,\ldots,x_{\log N-1})=\langle \vec{w},\vec{r}_0\otimes\vec{r}_1\rangle$ . Protocol 1 gives

#### **Protocol 1** Overview of Orion [XZS22] with simplifications

```

Public input: Evaluation point \vec{x} parsed as tensors \vec{r_0} and \vec{r_1};

Private input: Polynomial \phi with coefficients \vec{w}; Let E_C be the encoding function of

a [n, k, d] linear code and N = k^2;

1: function Commit(\phi)

▷ Similar to Brakedown

Parse the coefficient vector \vec{w} of length N as a k \times k-matrix W;

2:

Using E_C encode each row of W to obtain code C which is a k \times n matrix;

3:

for 0 \le i < n do

4:

Compute Merkle root for each column Root_i \leftarrow Merkle.Commit(C[:,i]);

5:

Compute the Merkle root \mathcal{R} \leftarrow \text{Merkle.Commit}([\text{Root}_0, \dots, \text{Root}_{n-1}]);

6:

7:

Output \mathcal{R} as the commitment;

8: function Prove(\phi, \vec{x}, \mathcal{R})

▷ Similar to Brakedown until line 13

Prover receives from the verifier a random vector \vec{\gamma}_0 \in \mathbb{F}_{p^2}^k;

\vec{c}_{\gamma_0} \leftarrow \sum_{i=0}^{k-1} \vec{\gamma}_0[i] \mathbf{C}[i,:], \ \vec{y}_{\gamma_0} \leftarrow \sum_{i=0}^{k-1} \vec{\gamma}_0[i] \mathbf{W}[i,:]; \vec{c}_1 \leftarrow \sum_{i=0}^{k-1} \vec{r}_0[i] \mathbf{C}[i,:], \ \vec{y}_1 \leftarrow \sum_{i=0}^{k-1} \vec{r}_0[i] \mathbf{W}[i,:]; Prover sends the evaluation of \phi at \vec{x} as y \leftarrow \langle \vec{y}_1, \vec{r}_1 \rangle to verifier;

10:

▷ Proximity check

▷ Consistency check

11:

* Starting here, Brakedown differs from Orion *

13:

Compute Merkle root \mathcal{R}_{\vec{c}_{\gamma_0}} \leftarrow \texttt{Merkle.Commit}(\vec{c}_{\gamma_0});

Compute Merkle root \mathcal{R}_{\vec{c}_1} \leftarrow \texttt{Merkle.Commit}(\vec{c}_1);

14:

/* The following message to the verifier forms Orion's proof string \pi_{\vec{x}} */

Prover sends \mathcal{R}_{\vec{c}_{\gamma_0}}, \mathcal{R}_{\vec{c}_1} to the verifier;

15:

Verifier sends the set \hat{I} of t (0 < t < n) randomly sampled column indexes;

16:

\pi_i \leftarrow \text{ZK.Prove}(): The prover executes a CP-SNARK ZK to prove the genuine vali-

17:

dation of the proximity and consistency checks. [Su] uses Virgo [ZXZS20] for this;

Send \pi_i to the verifier.

18:

19: function VerifyEval(\mathcal{R}, \vec{x}, y = \phi(\vec{x}), \pi_{\vec{x}}, \pi_i)

/* Verifier parses the proof string \pi_{\vec{\tau}} and \pi_i and obtains the prover's messages */

Verify the CP-SNARK ZK.Verify(\pi_i);

20:

Check consistency to \mathcal{R}_{\vec{c}_{\gamma_0}}, \mathcal{R}_{\vec{c}_1}, and \mathcal{R};

21:

22:

Accept if all checks pass;

```

an overview of Orion's polynomial commitment scheme [XZS22] with some simplifications and shows the similarities and differences to Brakedown [GLS<sup>+</sup>23].

**Commitment:** In line 2 of Protocol 1, the coefficient-vector  $\vec{w}$  of length  $N=k^2$  is parsed as the matrix  $\mathbf{W}$  of dimension  $k \times k$ . Note that the evaluation  $y=\phi(\vec{x})=\langle \vec{w}, \vec{r}_0 \otimes \vec{r}_1 \rangle$  can also be represented as a vector-matrix-vector multiplication as follows: the row-vector  $\vec{r}_0$  is multiplied from the left with the matrix  $\mathbf{W}$ , and the resulting row-vector is multiplied with the column-vector  $\vec{r}_1$  to produce y. Orion utilizes the tensor IOP protocol from [BCG20] to construct a polynomial commitment based on Brakedown [GLS<sup>+</sup>23].

Let  $E_C$  be the encoding procedure of an [n, k, d] linear code (Section 2.3). In line 3, each row  $\mathbf{W}[i,:]$  is encoded into a codeword of length n. After encoding all rows of  $\mathbf{W}$ , we obtain the code matrix  $\mathbf{C}$  of dimension  $k \times n$ . In lines 4 and 5, the columns of  $\mathbf{C}$  are Merkle-committed to leaf hashes  $\mathsf{Root}_i$ . Finally, from the n leaf hashes, the Merkle Tree is calculated in line 6 to produce the root hash  $\mathcal{R}$  as the final commitment to the tree. Orion and Brakedown use the linear-time Spielman code (described in the previous section) to achieve linear time complexity for the polynomial commitment. Moreover, Orion's and

Brakedown's commitment mechanisms are very similar, with only minor differences such as the underlying finite field. This allows applying our acceleration techniques for linear-time commitment to both schemes.

**Proving mechanism:** The prover and verifier engage in an interactive protocol starting from line 8 in Protocol 1. As a challenge, the verifier provides the prover with the random vector  $\vec{\gamma}_0 \in \mathbb{F}_{p^2}^k$ . Using  $\vec{\gamma}_0$ , in line 10 of the protocol, the prover computes random linear combinations of the rows of  $\mathbf{C}$  and  $\mathbf{W}$  via inner products. As the code is linear, any linear combination of codewords is also a codeword. Thus, if the calculations are performed correctly (i.e., non-cheating prover), the resulting codeword  $\vec{c}_{\gamma_0}$  should be the encoding of  $\vec{y}_{\gamma_0}$ . Next, in line 11, a similar linear combination is performed using  $\vec{r}_0$  of the tensor query  $\vec{r}_0 \otimes \vec{r}_1$ . If performed correctly,  $\vec{c}_1$  will be the encoding of  $\vec{y}_1$ .

Up to line 12, Orion and Brakedown follow very similar steps. Yet, from line 13 on, the two schemes differ. Brakedown directly sends  $\vec{c}_1$ ,  $\vec{y}_1$ ,  $\vec{c}_{\gamma_0}$ , and  $\vec{y}_{\gamma_0}$  to the verifier, which locally performs the so-called proximity check and consistency check. During these checks, the verifier encodes  $\vec{y}_{\gamma_0}$  and  $\vec{y}_1$  and ensures  $E_C(\vec{y}_{\gamma_0}) == \vec{c}_{\gamma_0}$  (proximity check) and  $E_C(\vec{y}_1) == \vec{c}_1$  (consistency check). In addition, the verifier randomly samples the set  $\hat{I}$  containing t column indices of  $\mathbf{C}$ . The prover sends the specified columns along with their Merkle proofs under the commitment  $\mathcal{R}$ . Finally, the verifier checks the obtained columns against  $\vec{c}_{\gamma_0}$  and  $\vec{c}_1$  and validates the Merkle proofs against  $\mathcal{R}$ . The verifier accepts if all checks succeed. The prover time complexity of Brakedown is  $\mathcal{O}(N)$ . However, the proof size is  $\mathcal{O}(\sqrt{N})$ , which is quite large compared to commonly used pairing-based proof systems.

Orion significantly reduces the proof sizes to  $\mathcal{O}(\log^2 N)$  by a so-called 'proof composition' technique [RZR24]. Orion's proof composition technique does not perform the consistency and proximity checks on the verifier side but on the prover side. Moreover, the prover ensures a genuine execution of these checks via a CP-SNARK ZK. This technique requires the prover to Merkle-commit to  $\vec{c}_{\gamma_0}$  and  $\vec{c}_1$ , as shown in lines 13 and 14 in Protocol 1. After the commitment has been sent to the verifier, the prover and the verifier execute the ZK protocol. The verifier finally checks the consistency of the Merkle commitments (line 21) and accepts if the checks succeed. Orion treats the CP-SNARK ZK as a black box; thus, any proper scheme can be used. The software implementation of Orion [Su] uses the Virgo [ZXZS20] protocol. Note that Brakedown does not involve any CP-SNARK at the cost of larger proof sizes.

**Generalization to**  $N = k_1 \cdot k_2$ : For simplicity, the above-mentioned description of encoding and Orion used  $N = k^2$ , resulting in  $\mathbf{W}$  of dimension  $k \times k$ . Assuming N is a power-of-two, it is easy to see that the same can be generalized to asymmetric decomposition  $N = k_1 \cdot k_2$ . The software implementation of Orion [Su] by the authors uses the fixed  $k_1 = 128$  for all large N. Depending on the value of N, the number of columns  $k_2$  in  $\mathbf{W}$  is adjusted. This gives flexibility. Following the authors of Orion, we use fixed  $k_1 = 128$  in our hardware implementation.

#### 3.3 Latency of Operations in Orion

In this section, we present a detailed latency analysis of Orion's core operations, particularly how the system's performance scales as N increases. Note that in contrast to other cryptographic schemes, such as the one-time key generation process in digital signatures, the commitment and proving phase in Orion is repeatedly invoked as part of a recursive proving system. For example, when creating proofs of training for Deep Neural Networks as in [APKP24], dedicated commitments are required for each layer. Each time the recursive prover processes a new layer or polynomial, it calls Orion to commit to the new data and

Table 1: Timing results in milliseconds (ms) of different operations in the reference implementation of Orion [Su]. Results collected in software on AMD EPYC 9754 @2.25GHz.

| $\mathbf{Size}\\ \log(N)$ | Prover's | s <b>Opera</b><br>Prove | tions in Orion<br>Commit+Prove | Virgo       | Total   | Verifier |

|---------------------------|----------|-------------------------|--------------------------------|-------------|---------|----------|

| 16                        | 40       | 4                       | 44                             | 37          | 81      | 43       |

| 18                        | 155      | 10                      | 165                            | 102         | 267     | 48       |

| 20                        | 701      | 35                      | 736                            | 483         | 1,219   | 56       |

| 22                        | 3,175    | 135                     | 3,310                          | 1,370       | 4,680   | 74       |

| 24                        | 14,756   | 593                     | 15,349                         | 5,849       | 21,198  | 131      |

| 26                        | 60,011   | 2,495                   | 62,506                         | $26,\!457$  | 88,963  | 218      |

| 28                        | 334,250  | 9,093                   | 343,343                        | $118,\!554$ | 461,897 | 211      |

Table 2: Timing breakdown for COMMIT suboperations in milliseconds (ms). Results collected in software [Su] on an AMD EPYC 9754 @2.25GHz.

| $\mathbf{Size}$ | Later      | Total                               |                                   |                            |         |

|-----------------|------------|-------------------------------------|-----------------------------------|----------------------------|---------|

| $\log(N)$       | Initialize | $\operatorname{Encode}(\mathbf{W})$ | $\operatorname{Hash}(\mathbf{C})$ | $Merkle\ Tree(\mathbf{H})$ | Commit  |

| 16              | 4          | 25                                  | 10                                | 1                          | 40      |

| 18              | 10         | 104                                 | 40                                | 1                          | 155     |

| 20              | 73         | 463                                 | 163                               | 2                          | 701     |

| 22              | 279        | 2,233                               | 656                               | 7                          | 3,175   |

| 24              | 1,998      | 10,080                              | 2,651                             | 27                         | 14,756  |

| 26              | 3,448      | $45,\!855$                          | 10,600                            | 108                        | 60,011  |

| 28              | 13,137     | 278,100                             | $42,\!580$                        | 433                        | 334,250 |

Table 3: Timing breakdown for Prove suboperations in milliseconds (ms). Results collected in software [Su] on an AMD EPYC 9754 @2.25GHz.

| Size      | Latencies     | of Sub-o                       | perations in Pro                             | ve    | Total |

|-----------|---------------|--------------------------------|----------------------------------------------|-------|-------|

| $\log(N)$ | Inner Product | $\operatorname{Hash}(\vec{c})$ | $\mathrm{Merkle}\ \mathrm{Tree}(\mathbf{H})$ | Other | Prove |

| 16        | 2             | 1                              | 1                                            | 0     | 4     |

| 18        | 8             | 1                              | 1                                            | 0     | 10    |

| 20        | 31            | 2                              | 2                                            | 0     | 35    |

| 22        | 120           | 7                              | 7                                            | 1     | 135   |

| 24        | 534           | 27                             | 27                                           | 5     | 593   |

| 26        | 2,262         | 106                            | 108                                          | 19    | 2,495 |

| 28        | 8,160         | 430                            | 433                                          | 70    | 9,093 |

perform the proof steps. As a result, the commitment and proving phases must efficiently handle repeated invocations, making it computationally intensive.

The computations in Orion can be broken down into three main phases: Commitment (lines 1-7 in Protocol 1), proving (lines 8-15), and the Virgo CP-SNARK (lines 16-21). Note that commitment and proving are executed solely by the prover, whereas Virgo, as the outer proof protocol, involves the prover and verifier. Table 1 presents a timing breakdown of the three phases collected using Orion's software implementation [Su]. While all phases contribute to overall latency, the commitment phase stands out due to its computational complexity, particularly in managing the polynomial commitments across recursive calls. Compared to commitment, the proving phase adds a smaller latency of up to 9 seconds for  $N=2^{28}$ . These two phases - commit and prove - define the latency of Orion, excluding the outer Virgo protocol, and cause the major share of 74% of the overall runtime  $(N=2^{28})$ . The Virgo column in Table 1 contains the latency for executing Virgo's prover protocol,

including circuit generation, circuit evaluation, sum-checks, etc. Hence, the Virgo prover causes around 26% of the overall latency. Finally, Table 1 shows the end-to-end latency of a full Orion execution including commit, prove, and the Virgo protocol, and the comparably low verifier latency.

The commitment phase stands out as the most time-intensive operation in Orion. This phase consists of several computationally demanding sub-operations, including initialization, linear encoding, hashing, and Merkle Tree generation. Table 2 presents the software latencies of these sub-operations. Therein, the initialization phase plays a crucial role in constructing expander graphs, which are essential for establishing the system's foundational structure. The most prominent operation, however, is linear encoding, which takes the input and encodes it using expander graphs. The encoding process, as well as expander graphs, are described in detail in Section 2.3. Following the encoding, the hashing of the columns of the encoded matrix C for Merkle Tree construction represents the second largest time cost. Note that Orion's software implementation supports SHA2 and SHA3 algorithms, where we choose the more recent SHA3 setting for all benchmarks.

Orion's proving phase (lines 8-14 in Protocol 1) consists of the inner product computation, hashing, and Merkle Tree generation. In addition, smaller operations such as tensorization, evaluation computation, etc., are grouped into an 'Other' category. The latencies of these sub-operations are reported in Table 3. We observe that the inner product computation is the prevailing operation within proving, whereas hashing and Merkle Tree generation are more lightweight.

Operations we target for hardware acceleration: This work targets the most demanding computations within the Orion scheme and presents FPGA acceleration techniques for Orion and Brakedown-like PCS. Our design offers support for on-the-fly graph generation, thereby omitting the initialization sub-operation and avoiding storing the large graph in memory. Moreover, we address the challenging linear encoding using Spielman codes and present hardware-oriented optimizations. We also include units for hashing and Merkle Tree computations needed in the commitment and proving steps. Finally, we reuse the datapath for linear encoding to accelerate the inner product computation during proving. These measures effectively improve the runtime of the commitment and proving steps.

While our paper presents a deep design exploration and hardware optimization of Orion- and Brakedown-like commitment and proof generation components, it excludes the acceleration of the higher-level Virgo protocol from its scope. The Virgo protocol integrates multiple complex mechanisms, including sum-check protocols [LFKN92], GKR protocols [GKR15], and arithmetic circuit transformations. Each of these components introduces distinct computational patterns and design challenges. Consequently, accelerating the full Virgo protocol requires substantial additional research beyond the scope of this work. Nevertheless, extending hardware acceleration to encompass an entire CP-SNARK system such as Virgo remains an exciting direction for future investigation.

# 4 Accelerating Expander Graph based Linear Encoding

The linear-time commitment and proof generation in Orion and Brakedown stems from their expander-based linear encoding as covered in Section 2.2. These graphs are carefully designed to be sparse, with a limited number of edges per node, while maintaining high connectivity to preserve the security and succinctness required for cryptographic protocols. This dual property is essential because the sparsity ensures efficient computations, while high connectivity guarantees the soundness of encoding.

The straightforward process of constructing and using expander graphs involves Gigabytes of storage and random accesses to off-chip memory. Random accesses substantially lower the off-chip memory bandwidth [Xil24], as discussed in Section 2.5. In addition,

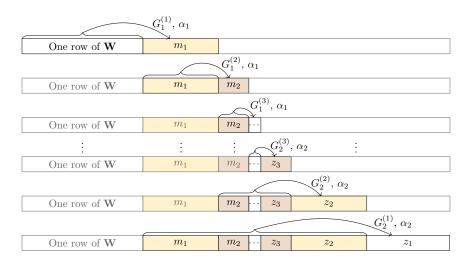

Figure 4: Our iterative approach for computing Spielman codes. The example has 3 levels.

frequent read and write interleavings during graph evaluations, as used in the reference software implementation [Su], cause significant turnaround overheads in the DRAM-based off-chip memory systems.

Our hardware accelerator tackles these off-chip data movement challenges through a holistic design approach. The remainder of this section presents our suite of novel optimizations for efficient and hardware-friendly linear encoding using expander graphs. We begin by discussing the advantages of on-the-fly graph generation and our custom iterative encoding procedure. Next, we introduce *inverted expander graphs*, which significantly reduce the random off-chip memory accesses and read-write turnarounds. We also detail the non-trivial integration of on-the-fly graph generation with the graph inversion technique. Finally, we describe our memory-bandwidth-aware accelerator architecture tailored for high-throughput linear encoding.

#### 4.1 On-the-Fly Graph Sampling

In the baseline software implementation of Orion [Su], the entire expander graph is first randomly sampled according to Algorithm 2 and then stored in memory before its usage. Storing the sampled graph, however, causes a substantial memory consumption. For example, a  $N=2^{28}$  polynomial, which needs 8 recursions and hence 16 different graphs, consumes 1.1 GiB. Storing this data requires additional off-chip memory resources such as DDR RAM. Also, although reading the graph from memory follows a linear pattern, scarce off-chip bandwidth is consumed.

However, the used expander graphs are public and randomly sampled (see Section 2.2.2). This allows for resampling the graphs on the fly during each encoding. Therefore, we use a pseudo-random number generator (PRNG) to expand the needed graphs based on a public seed. Note that using a PRNG with a sufficiently high period for graph sampling does not compromise security; it is just used to deterministically sample public data. In our implementation, we use the Trivium [Bou20] PRNG with a period  $> 2^{90}$ . This allows for the dynamic construction of large parts of the expander graphs during the encoding process.

#### 4.2 Iterative Linear Encoding

Orion encodes the coefficient matrix  $\mathbf{W}$  of a polynomial into a code matrix  $\mathbf{C}$  in a row-wise manner. In essence, each row in  $\mathbf{W}$  is encoded into one row of  $\mathbf{C}$  as detailed in Section 3.2. In the software implementation of Orion, the linear encoding algorithm for one row in  $\mathbf{W}$  is recursive, as discussed in Section 2.3. Yet, a recursive approach is not ideal for hardware designs due to increased control overhead. Thus, we implement linear encoding iteratively, as shown in Figure 4.

The iterative linear encoding procedure starts with applying an expander graph  $G_1^{(1)}$  with compression parameter  $\alpha_1 < 1$  to the input message, which is one row of **W** (Figure 4 top). The result of this operation is  $m_1$ , which is smaller in size than the input message. In the next step, another expander graph  $G_1^{(2)}$  with  $\alpha_1$  is applied on  $m_1$  yielding  $m_2$ . Thereby,  $m_2$  is again smaller than  $m_1$ . This procedure is applied until the size of  $m_i$  is below a certain threshold  $n_0$ .

Thereafter, different expander graphs  $G_2^{(j)}$  with compression parameter  $\alpha_2 < 1$  are applied iteratively on the previous codewords, as shown in Figure 4. The results of the  $G_2^{(j)}$  expanders are denoted with  $z_j$ . The  $G_2^{(j)}$  graph evaluations are repeated until all previous intermediate codewords are consumed. According to Section 2.3,  $\alpha_1$  and  $\alpha_2$  are given by the code parameter  $\alpha$  which is  $\alpha = 0.238$  in Orion [Su]. We obey this configuration in our work. The final expander graph evaluation  $G_2^{(1)}$  yields  $z_1$ , which completes the linear encoding.

# 4.3 Optimizing Memory Bandwidth with Inverted Expander Graphs

Traversing expander graphs involves irregular and random memory access patterns, creating performance bottlenecks when working with large datasets stored in external memory such as DDR or HBM. These random accesses can degrade memory bandwidth by up to  $3\times$  (see Section 2.5), and frequent read-write turnarounds further increase latency. The reference implementation [Su] does not mitigate these overheads.

To overcome these limitations, we propose an *inverted expander graph* that reduces random memory accesses and minimizes read-write turnarounds, thereby improving overall performance. This section begins with a review of the baseline implementation [Su], highlighting its inefficiencies for hardware. We then introduce our inverted approach, analyze its impact on memory bandwidth, and discuss its security implications.

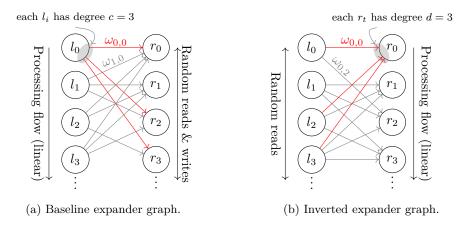

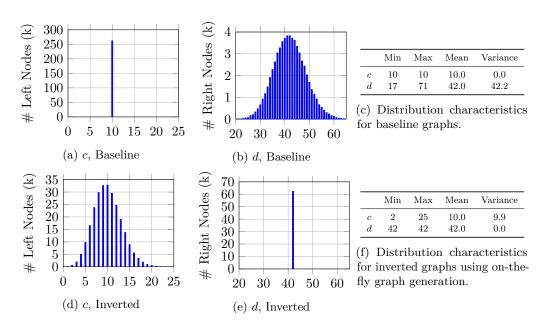

#### 4.3.1 The Baseline Expander Graph Evaluation and their Disadvantages

The baseline expander graph evaluation (e.g., as implemented in [Su]) is illustrated in Figure 5a. The expander graph G=(L,R,E) is represented by two node arrays  $L=\{l_0,l_1,\ldots\}$  and  $R=\{r_0,r_1,\ldots\}$ , where the values of nodes  $l_i,r_t\in\mathbb{F}_{p^2}$ . Each left-side node  $l_i$  has a fixed degree c (c=3 in Figure 5a, c=10 in [Su]), and a connecting edge between  $l_i$  and  $r_t$  carrying a random weight  $\omega_{i,t}\in\mathbb{F}_{p^2}$ . The degree of right-side nodes  $r_t$  varies due to the randomized left-to-right node assignments, leading to a binomial distribution of edge counts across R (Figures 6a–6c). All  $r_t$  are initialized to zero. During evaluation, each  $l_i$  is processed sequentially: it is multiplied by its c associated edge weights and accumulated into the corresponding  $r_t$  nodes. For example, as highlighted in red in Figure 5a,  $l_0$  updates  $r_0$ ,  $r_2$ , and  $r_3$  as follows:

$$r_0 = r_0 + l_0 \cdot \omega_{0,0}$$

$r_2 = r_2 + l_0 \cdot \omega_{0,2}$   $r_3 = r_3 + l_0 \cdot \omega_{0,3}$  (3)

Importantly, the left-side nodes are accessed in a linear order, while the right-side nodes are accessed in a randomized order. This approach of graph evaluation requires random read and write operations, which lowers the effective memory bandwidth. For each input

Figure 5: The two different approaches of expander graph implementation. Only a few weights  $\omega_{i,t}$  are explicitly shown, but every edge connecting  $l_i$  to  $r_t$  has a weight  $\omega_{i,t}$ .

node  $l_i$ , c random right-nodes  $r_{t_1}$  to  $r_{t_c}$  must be read from off-chip memory, as storing the large data structure on the chip is infeasible. Then, the c accumulations are performed (as in Equation 3), and the c results are stored back in scattered memory locations. In this way, per input node  $l_i$ , c random reads and c random writes are required. For a whole graph evaluation of G = (L, R, E), |L| linear reads, |E| random reads, and |E| random writes must be performed.

Table 4 reports the off-chip memory access count for the full encoding process with multiple graph evaluations. For the baseline expander graphs, up to 104 million read and write operations are required to load and store the actual codeword data. Moreover, up to 50 million additional read operations would be required to load the graph structure from memory. This high number of non-uniform memory accesses is challenging even for HBM. While HBM offers a high theoretical peak bandwidth, the effective bandwidth is significantly lower due to random access patterns as explained and detailed in Section 2.5.

In addition to random memory accesses, the graph evaluation approach introduces read-after-write hazards in the multiplication and accumulation pipeline. Consider two consecutive input nodes  $l_i$  and  $l_{i+1}$  mapping to the same output node  $r_t$ , which is likely to occur in expanders with few right nodes |R|. In such cases, the write operation updating  $r_t$  from  $l_i$  must complete before the subsequent read by  $l_{i+1}$  can proceed. While these dependencies can be efficiently managed in fully on-chip designs using techniques like data forwarding or buffering, they become significantly more problematic when using off-chip memory, due to higher latency and the lack of immediate write visibility. As a result, the pipeline must stall to ensure correctness, leading to increased control logic complexity and reduced throughput. These stalls, combined with inefficient memory access patterns, substantially degrade the performance of the baseline expander graph evaluation. The next section presents our optimized solution to address these bottlenecks.

#### 4.3.2 Inverted Expander Graph Evaluation for Minimizing Memory Accesses

We propose an inverted expander graph evaluation that reverses the baseline approach from Section 4.3.1, which processes the *left* nodes sequentially to distribute values to the right nodes. Instead, our inverted method iterates over the *right* nodes, aggregating contributions from connected left nodes, as shown in Figure 5b. For example, to compute  $r_0$ , the evaluation loads the d=3 connected left nodes  $l_0$ ,  $l_2$ , and  $l_3$ , then multiplies each by its respective weight and accumulates the results. Once  $r_0$  is computed, the process moves to  $r_1$ , repeating the same steps.

Table 4: Off-chip read and write operations for linear encoding using baseline expander graphs and our inverted expander graphs with approach 1 and approach 2. GRd refers to off-chip reads to obtain the stored graph structure.

|                      |         |                 | ander Gra          | Inverted Expander Graphs |         |                     |           |             |             |                 |           |      |

|----------------------|---------|-----------------|--------------------|--------------------------|---------|---------------------|-----------|-------------|-------------|-----------------|-----------|------|

| $\tilde{\mathbf{z}}$ | I.      | eft to Rig.     | ht Evaluatio       | n                        |         |                     | Ri        | ght to Left | t Evaluatio | on              |           |      |

|                      |         | Stored          | l Graph            |                          | App     | oroach 1:           | Stored Gr | aph         | Appr        | oach 2: S       | Sampled G | raph |

| log                  | #Rd     | $\#\mathrm{Wr}$ | #Total             | #GRd                     | #Rd     | #Rd #Wr #Total #GRd |           |             | #Rd         | $\#\mathrm{Wr}$ | #Total    | #GRd |

| 16                   | 12,773  | 11,850          | 24,623             | 11,850                   | 12,048  | 368                 | 12,416    | 11,850      | 13,151      | 1,196           | 14,347    | 0    |

| 18                   | 52,253  | 48,490          | 100,743            | 48,490                   | 48,484  | 1,474               | 49,958    | 48,490      | 53,251      | 5,070           | 58,321    | 0    |

| 20                   | 210,267 | 195,140         | 405,407            | 195,140                  | 194,212 | 5,898               | 200,110   | 195,140     | 213,754     | 20,752          | 234,506   | 0    |

| 22                   | 842,154 | 781,580         | 1,623,734          | $781,\!580$              | 777,024 | 23,592              | 800,616   | $781,\!580$ | 855,308     | 83,028          | 938,336   | 0    |

| 24                   | 3.37M   | 3.13M           | 6.50M              | 3.13M                    | 3.11M   | 0.09M               | 3.20M     | 3.13M       | 3.42M       | 0.33M           | 3.75M     | 0    |

| 26                   | 13.48M  | 12.51M          | 25.99M             | 12.51M                   | 12.43M  | 0.38M               | 12.81M    | 12.51M      | 13.68M      | 1.33M           | 15.01M    | 0    |

| 28                   | 53.93M  | 50.05M          | $103.98\mathrm{M}$ | 50.05M                   | 49.74M  | 1.51M               | 51.25M    | 50.05M      | 54.74M      | 5.31M           | 60.05M    | 0    |

Our inverted expander graphs remove the read-after-write hazards and reduce the penalty of memory accesses in a G=(L,R,E) graph evaluation. In particular, just |R| linear write operations are needed whereas baseline graphs require |E| random writes (note that  $|E|\gg |R|$ ). In addition, |L| linear reads are saved, and frequent read-write turnarounds are avoided.

How to deploy inverted expander graphs: Although the described inverted expander graphs significantly lower the random memory accesses, they cannot be directly combined with on-the-fly graph sampling. This is because the binomially distributed right node degree d and the corresponding edges to left nodes are not computable via a PRNG such that each left node has a constant degree c (as it is the case in baseline graphs, see Figures 6a to 6c). Instead, two different approaches can be applied:

- 1. Storing the graph structure in memory: In this approach, a baseline graph is generated using Algorithm 2. This graph is then reordered from left-node major order to right-node major order, where all connections of one right node are stored consecutively. The resulting graph is kept in off-chip memory and streamed to the hardware architecture, which computes the inverted graph evaluation.

- 2. **Relaxing the left-node degree** c: This approach samples the inverted expander graph structure on-the-fly using a PRNG and directly evaluates the inverted graph. Specifically, we fix the right node degree d and iterate linearly over the right nodes. For each right node, the PRNG randomly selects d left nodes, accumulating the right node. This leads to a constant degree of right nodes and a binomially distributed degree of left nodes c. Figures 6d to 6f show examples of the corresponding distributions.

The encoding in approach 1 yields the identical result as Orion's or Brakedown's baseline implementations, but also has the drawback of high off-chip memory consumption as both the graph and data must be accessed. Table 4 shows the resulting off-chip memory accesses. Compared to baseline graphs, our inverted graphs with approach 1 clearly reduce the data reads and writes by about 50% (column #Total). Nevertheless, the data movements still take place in the range of Gigabytes. In addition to the encoding data, the graph structure must also be loaded from off-chip memory in approach 1. Loading the graph structure causes almost as many reads as the actual data streaming (see column #GRd in Table 4). Hence, storing the graph in HBM would degrade the effective memory bandwidth during linear encoding since reading the graph structure blocks the data reads and writes. Using supplementary DDR memory for storing the graph structure is also problematic since FPGAs like Alveo U55C [Xil23] or [Xil21] do not have DDR memory. Thus, it is desirable not to store the graph structure but to generate it on the fly.

On the other hand, approach 2 changes the structure of the Spielman code, yielding a different encoding result compared to the baseline implementation. This difference, however, is *transparent* to the verifier due to Orion's proof composition technique (see

Figure 6: Distributions of left and right node degree c and d for baseline graphs and inverted expander graphs using on-the-fly graph sampling. Parameters for Orion's  $G_1$  graph.

Section 3.2). In particular, the verifier never performs the encoding themself but only verifies the outer Virgo proof and Merkle commitments. Hence, the verifier remains unaffected by our proposed approach 2. In addition, approach 2 combines the benefits of on-the-fly graph sampling (i.e., avoiding graph storage in off-chip memory and not relying on DDR in linear encoding) with inverted expander graph evaluation (reduced HBM accesses). This makes approach 2 more interesting for high-performance hardware architectures and inspires us to design our hardware using approach 2. Yet, changing our design to approach 1 is possible given that the target FPGA provides sufficient off-chip memory and bandwidth. The PRNG queries must be replaced by off-chip memory reads, which requires data routing across the FPGA. This data routing requires engineering effort to place and route the additional logic within the dense design. Hence, we will present estimated timing benchmarks for approach 1 in the result section (Section 7.4) and actual latencies for our FPGA design using approach 2. In the remainder of this section, we will solely focus on our inverted expander graphs using approach 2.

How to mitigate low-degree left nodes in approach 2: The inverted expander graph with on-the-fly sampling connects a right node with d left nodes randomly, as described in Runexpander of Algorithm 1. While the right nodes have the fixed degree d, this random sampling causes the left node degree c to follow a binomial distribution (Figure 6d), unlike the baseline graph. Hence, there are left nodes with fewer connections (i.e., degree lower than c), and this can compromise the minimal distance guarantees of the linear code. We address this issue using a postprocessing step (function Postprocess in Algorithm 1). Postprocessing is executed after the inverted expander graph evaluation and adds additional connections from low-degree left nodes to right nodes of the public graph. These additional connections leverage the left node's degree to meet a certain lower bound. Satisfying this lower bound on the left node degree leads to sufficient connectivity and code distance, as will be shown in Section 4.3.3. Yet, introducing additional connections to left nodes causes a small amount of additional computations. This is reflected in the number of data reads

**Algorithm 1** Our on-the-fly inverted expander graph evaluation with postprocessing.

```

1: function RUNEXPANDER(L, k, \alpha_i, d, \text{seed}, W)

\triangleright L = [l_0, \dots, l_{k-1}] left nodes

\triangleright d is degree of right-side nodes

PRNG.Init(seed)

2:

▶ Number of right-side nodes

3:

q \leftarrow \alpha_i k

for t from 0 to q-1 do

\triangleright Iterate over all right-side nodes r_t

4:

r_t \leftarrow 0

5:

for j from 0 to d-1 do

\triangleright Find d many random left-side nodes l_i

6:

i \leftarrow \mathtt{PRNG.Random}() \mod k

\triangleright Random node index for L

7:

\omega_{i,t} \leftarrow \mathtt{PRNG}.\mathtt{FieldRandom}()

\triangleright Random field element

8:

r_t \leftarrow r_t + l_i \cdot \omega_{i,t}

9:

▷ Field multiplication with the value of left node

10:

R \leftarrow [r_0, \dots, r_{q-1}]

return PostProcess(L,R,W)

11:

12: function PostProcess(L, R, W)

\triangleright W: list of low-degree left nodes

for each (i, n_{rs}) \in W do

\triangleright Node l_i requires n_{rs} additional connections

13:

for j from 0 to n_{rs} - 1 do

\triangleright Find n_{rs} many random right-side nodes r_t

14:

t \leftarrow \mathtt{PRNG.Random}() \mod \alpha_i k

15:

\omega_{i,t} \leftarrow \texttt{PRNG.FieldRandom}()

16:

l_i \leftarrow L[i], r_t \leftarrow R[t]

17:

r_t \leftarrow r_t + l_i \cdot \omega_{i,t}

\triangleright Add connection from l_i to r_t

18:

R[t] \leftarrow r_t

19:

return R

20:

```

and writes in Table 4. Compared to inverted graphs with approach 1, about 17% more read and write operations are required, but graph reads from off-chip memory are entirely avoided.

We precompute and store the addresses of the low-degree left nodes for the selected PRNG seed and store them in memory. Unlike storing the whole graph consuming Gigabytes, this postprocessing information is small enough to fit into on-chip memory. This eliminates the need for external DDR memory and enables linear encoding on DDR-less FPGAs. Overall, our inverted expander graphs effectively reduce the memory accesses to HBM and allow for performant linear encoding. In our design, the inverted graph evaluation causes about 82.5% of the linear encoding runtime, whereas postprocessing accounts for about 17.5% of the runtime, as discussed in Section 6.2. Importantly, our on-the-fly graph sampling and postprocessing do not require off-chip memory to store the large graph.

#### 4.3.3 Security Analysis of Inverted Expander Graphs

The expander graph evaluation in Orion and Brakedown proof systems implements a linear error-correcting encoding that detects malicious alterations in the coefficient matrix  $\mathbf{W}$  by a cheating prover. To ensure security, the underlying [n,k,d] linear code must have a sufficiently high relative distance  $\delta$ , which intuitively guarantees strong diffusion, meaning small changes in the input significantly impact the encoded output. In this section, we demonstrate that our proposed encoding strategy based on inverted expander graphs and postprocessing maintains this crucial relative distance property. Specifically, by enforcing a minimal left-node degree greater than or equal to the fixed degree of baseline Orion's codes, our encoding achieves, with overwhelming probability, at least the same relative distance as the original Orion encoding [XZS22]. This result similarly applies to the parameter sets used in the Brakedown proof system [GLS<sup>+</sup>23]. While a detailed formal

proof is provided later, this intuitive explanation highlights the rationale behind ensuring a minimum left-node degree to preserve encoding security.

For this analysis, we recall the functionality of Spielman codes as explained in Section 2.3 and Figure 2. To compute the [n,k,d] Spielman code  $E_C(\vec{x})$  of message  $\vec{x} \in \mathbb{F}_q^{k\dagger}$ , the expander graph  $G_1$  with compression factor  $\alpha_1 = \alpha$  is applied to  $\vec{x}$  yielding  $\vec{m}_1 = G_1(\vec{x}) \in \mathbb{F}_q^{\alpha k}$ . Then, a recursive  $[\alpha n, \alpha k, \alpha d]$  Spielman encoding  $\vec{y}_1 = E_C^{\rm rec}(\vec{m}_1)$  with relative distance  $\delta$  is computed using the same strategy. The intermediate result  $\vec{y}_1$  is the input to the second graph evaluation  $\vec{z}_1 = G_2(\vec{y}_1)$ , having compression factor of  $\alpha_2$ . The overall Spielman codeword  $E_C(\vec{x}) = (\vec{x} \parallel \vec{y}_1 \parallel \vec{z}_1)$  is the concatenation of  $\vec{x}$ ,  $\vec{y}_1$ , and  $\vec{z}_1$ .

Using this construction, Brakedown in [GLS<sup>+</sup>21] shows that a [n,k,d] Spielman encoding  $E_C(\vec{x})$  with parameter  $\alpha$  and rate r=n/k reaches a relative distance  $\delta=d/n$  with overwhelming probability if all left nodes in  $G_1$  and  $G_2$  have a constant degree of  $c_{1,\mathrm{BD}}$  and  $c_{2,\mathrm{BD}}$  as computed in Equation 4 and Equation 5, respectively. Therein,  $H(\cdot)$  denotes the binary entropy function,  $\mu=r-1-r\alpha$ , and  $\nu=\delta r+\alpha\delta r+0.03$ .

$$c_{1,\text{BD}} = \left\lceil \min\left(\max(1.28\delta n, \delta n + 4), \frac{1}{\delta r \log \frac{\alpha}{1.28\delta r}} \left(\frac{110}{k} + H(\delta r) + \alpha H(\frac{1.28\delta r}{\alpha})\right)\right) \right\rceil$$

(4)

$$c_{2,\text{BD}} = \left\lceil \min\left(2\delta n + \frac{n - k + 110}{\log p^2}, D\right) \right\rceil$$

(5)