# An Optimized Instantiation of Post-Quantum MQTT protocol on 8-bit AVR Sensor Nodes

## YoungBeom Kim

Kookmin University Seoul, Republic of Korea darania@kookmin.ac.kr

# Seog Chung Seo\* Kookmin University

Seoul, Republic of Korea scseo@kookmin.ac.kr

#### Abstract

Since the selection of the National Institute of Standards and Technology (NIST) Post-Quantum Cryptography (PQC) standardization algorithms, research on integrating PQC into security protocols such as TLS/SSL, IPSec, and DNSSEC has been actively pursued. However, PQC migration for Internet of Things (IoT) communication protocols remains largely unexplored. Embedded devices in IoT environments have limited computational power and memory, making it crucial to optimize PQC algorithms for efficient computation and minimal memory usage when deploying them on low-spec IoT devices. In this paper, we introduce KEM-MQTT, a lightweight and efficient Key Encapsulation Mechanism (KEM) for the Message Queuing Telemetry Transport (MQTT) protocol, widely used in IoT environments. Our approach applies the NIST KEM algorithm Crystals-Kyber (Kyber) while leveraging MQTT's characteristics and sensor node constraints. To enhance efficiency, we address certificate verification issues and adopt KEMTLS [71] to eliminate the need for Post-Quantum Digital Signatures Algorithm (PQC-DSA) in mutual authentication. As a result, KEM-MQTT retains its lightweight properties while maintaining the security guarantees of TLS 1.3. We identify inefficiencies in existing Kyber implementations on 8-bit AVR microcontrollers (MCUs), which are highly resource-constrained. To address this, we propose novel implementation techniques that optimize Kyber for AVR, focusing on high-speed execution, reduced memory consumption, and secure implementation, including Signed LookUp-Table (LUT) Reduction. Our optimized Kyber achieves performance gains of 81%,75%, and 85% in the KeyGen, Encaps, and DeCaps processes, respectively, compared to the reference implementation. With approximately 3 KB of stack usage, our Kyber implementation surpasses all stateof-the-art Elliptic Curve Diffie-Hellman (ECDH) implementations. Finally, in KEM-MQTT using Kyber-512, an 8-bit AVR device completes the handshake preparation process in 4.32 seconds, excluding the physical transmission and reception times.

#### **CCS** Concepts

Security and privacy → Embedded systems security;

$^{\star}$ Corresponding Author.

This work is licensed under a Creative Commons Attribution 4.0 International License. ASIA CCS '25, August 25–29, 2025, Hanoi, Vietnam © 2025 Copyright held by the owner/author(s). ACM ISBN 979-8-4007-1410-8/2025/08 https://doi.org/10.1145/3708821.3733873

## **Keywords**

Post-Quantum Cryptography, Kyber, 8-bit AVR, Modular Arithmetic, IoT device, Lightweight protocol, MQTT, ML-KEM

#### **ACM Reference Format:**

YoungBeom Kim and Seog Chung Seo. 2025. An Optimized Instantiation of Post-Quantum MQTT protocol on 8-bit AVR Sensor Nodes. In ACM Asia Conference on Computer and Communications Security (ASIA CCS '25), August 25–29, 2025, Hanoi, Vietnam. ACM, New York, NY, USA, 19 pages. https://doi.org/10.1145/3708821.3733873

## 1 Introduction

The advancement of quantum computing poses a significant threat to widely used public-key cryptographic systems such as RSA and Elliptic Curve Cryptography (ECC)-based Digital Signature Algorithm (DSA) [77, 78]. Currently, quantum computers have reached 127 qubits, and it is expected that within the next 20 years, quantumbased cryptographic attacks will become a reality [49, 67]. In response, the National Institute of Standards and Technology (NIST) launched the Post-Quantum Cryptography (PQC) standardization process at PQCrypto 2016, inviting proposals for PQC standards. In the past year, four algorithms (Crystals-Kyber [9], Crystals-Dilithium [8], Falcon [63], and SPHINCS+ [35]) were selected as PQC standards. Among these, Kyber is the sole Key Encapsulation Mechanism (KEM) for key establishment, while Dilithium, Falcon, and SPHINCS+ are Digital Signatures Algorithms (DSAs). Initially, PQC research primarily on cryptanalysis. However, after the Round 3 finalists were announced, the focus shifted toward practical deployment and optimization. Security professionals often raise two key questions regarding PQC adoption:

- Q1: Is PQC more efficient than ECDH and ECDSA?

- Q2: Is it necessary to migrate to PQC now?

Regarding the first question, performance studies on Kyber indicate that with proper optimization, it can outperform the elliptic curve Diffie-Hellman (ECDH). This efficiency stems from Kyber's ability to performs modular multiplication at the machineword level, making it well-suited for parallel processing. Optimized implementations demonstrate superior performance compared to the latest ECC implementations on platforms such as Cortex-M4 [2, 33], Cortex-A [14], RISC-V [34], and AVX2 [73], as well as in TLS 1.3 handshake performance tests [60]. Over the past eight years, researchers have continuously refined PQC implementations for embedded devices, introducing new optimization techniques [2, 4, 14, 16, 20, 29, 33, 34, 37, 43]. A key observation is that architecture-specific optimization is essential: for instance, state-of-the-art modular multiplication techniques vary across AVX2 [73], Cortex-A [14], and Cortex-M4 [33].

Without such optimizations, reference implementations of Kyber impose excessive computational overhead on Internet of Things (IoT) devices, underscoring the necessity of tailored approaches for new architectures.

While large-scale quantum computers remain years away, the second question remains critical. A well-known concern is the "store now, decrypt later" attack [64]. If ECDH is eventually broken by quantum computers, session keys from past communications could be recovered-even if forward secrecy was applied [71]. Therefore transitioning to PQC is imperative. Fortunately, extensive efforts have already been made to prepare security protocols-including TLS/SSL [60], SSH [23], and IPSec [10].

Despite these advancements, most existing PQC research has focused on specific architectures. Studies have primarily targeted embedded devices with 32-bit processors, such as 32-bit Cortex-M3/M4 and RISC-V [2, 4, 16, 33, 34, 84], or high-performance processors like 64-bit ARMv8 [14, 43, 44] and AVX2-based systems [73]. However, research on architectures with register sizes smaller than 32-bit, including 8-bit AVR and 16-bit MSP430, remains limited. Similarly, previous studies on PQC protocol migration have primarily focused on security protocols for desktop and server-class processors (x86/64) or high-performance ARM Cortex-A devices [3, 10, 23, 31, 60, 66, 69]. However, low-resource IoT environments require not only protocol migration but also PQC optimization tailored to constrained hardware. The 8-bit AVR microcontroller features a simple single-stage pipeline architecture and 32 general-purpose registers, each 8 bits in size [52]. Although it supports 8-bit multiplication instructions, the absence of advanced arithmetic units such as a barrel shifter imposes significant constraints when implementing cryptographic algorithms [7], especially in comparison to mid-range embedded systems like the Cortex-M series.

This challenge was highlighted at the 3rd PQC Standardization Conference [6] and in recent surveys [64], which emphasized the growing demand for 16-bit processors (MSP430) and 8-bit microcontrollers (AVR) while noting the lack of PQC research for these platforms. Currently, 32-bit ARM processors dominate the highperformance embedded systems market due to their computational power and mature software ecosystem. However, 8-bit AVR microcontrollers remain widely used in cost-sensitive, ultralow-power applications, such as sensor nodes, industrial control systems, and home automation [5, 56]. The simplicity of AVR architecture enables predictable execution timing and lower power consumption, making it preferable for power-constrained deployments [17, 65]. In large-scale sensor networks deployed in physically inaccessible environments—such as military applications or wildfire detection low-cost, low-power architectures are essential, and 8-bit AVR remains a viable solution [41, 42]. However, there have been few reported PQC implementations on small sensor nodes like 8-bit AVR [18, 37], despite their potential vulnerability as weak links once quantum computers become practical. Currently, answering the first question for AVR is infeasible. Since PQCrypto 2016, implementations of the NIST PQC algorithms have not been able to efficiently run on 8-bit AVR microcontrollers [37]. For example, the ATmega4808 core of the AVR-IoT WG Development board, commonly used as a sensor node, has only 6 KB of SRAM and 48 KB of flash memory [52]. Thus, it is crucial to first determine whether PQC, with its larger key and ciphertext sizes, is even viable in

such resource-constrained environments [39]. Additionally, protocol memory requirements must be assessed, and PQC should not be prohibitively slow compared to ECDH/ECDSA.

The second question must be framed differently for AVR. As demonstrated by the Padding Oracle On Downgraded Legacy Encryption (POODLE) attack [25, 54], failing to migrate AVR-based systems to PQC could create downgrade attack vectors, even if servers adopt PQC. Ensuring PQC compatibility on resourced-constrained devices mitigates future downgrade attacks targeting these endpoints. While some may argue that 8-bit AVR should be phased out, this would be an extreme solution.

This paper addresses both key questions for 8-bit AVR sensor nodes, the most resource-constrained embedded devices. First, we propose the KEM-MQTT protocol, demonstrating that PQC protocol migration is practically feasible on 8-bit AVR. KEM-MQTT uses only Kyber to perform mutual authentication without certificates and provides security properties such as confidentiality, integrity, and non-repudiation. This is the first practical PQC migration on 8-bit AVR, designed for IoT environments. Furthermore, we demonstrate the feasibility of implementing Kyber on 8-bit AVR, showing that Kyber can be implemented more securely and efficiently than ECDH with minimal memory usage.

#### **Contributions.** We summarize our main contributions below:

- Presenting KEM-MQTT for Quantum-Secure WSNs on AVR:

We have concluded that it is practically impossible to implement even highly optimized versions of Dilithium, Falcon, and SPHINCS+ on AVR. To ensure non-repudiation, we adopted the KEMTLS [28, 71, 72] approach instead of using PQC-DSA. By considering the characteristics of MQTT and AVR sensor nodes, we addressed the issue of certificate verification and ultimately proposed a new protocol called KEM-MQTT. KEM-MQTT maintains the security properties of TLS 1.3 and additionally provides mutual authentication. The handshake of KEM-MQTT (HKDF, AEAD, etc.) was manually implemented with hand-written assembly, excluding physical transmission and reception.

- $\bullet \ \textit{Presenting the first Kyber implementations on AVR}:$

- We applied the streaming method proposed in [16] to Kyber, implementing all security levels of Kyber with approximately 3KB of stack usage. After thoroughly reviewing and directly implementing state-of-the-art modular multiplication techniques proposed in various architecture, we concluded that they are not suitable for the 8-bit AVR environment. Consequently, we propose Kyber implementation methodologies, including the Signed LookUp-Table (LUT) Reduction techniques for modular multiplication, to surpass ECDH. As a result, compared to the latest P-256-based ephemeral ECDH implementation, the Kyber-512 implementation with the same security level is 37.5% faster (reducing execution time by 1.5 seconds). Additionally, Kyber-768, a mid-term security measure, guarantees performance nearly identical to the P-256-based ephemeral ECDH. Our technique is readily adaptable to ML-KEM [58] and requires no significant modifications.

• Presenting protocol-friendly Kyber software on AVR: We propose a Prehashed Public-Key technique to accelerate Kyber's encapsulation in KEM-MQTT and a flexible LUT placement strategy for adapting to different AVR board configurations. Additionally, we introduce three implementation methodologies. (i) High-Speed: The optimization methods used for NTT-based polynomial multiplication in state-of-the-art implementations are either inefficient or difficult to apply in the AVR environment. To overcome this, we employ Karatsuba multiplication and the GS butterfly technique, while also introducing a new approach called crossed-butterfly.

(ii) Low-Memory: Based on [16], we present a method to implement Kyber on AVR with minimal memory usage.

(iii) Secure Implementation: All our code meets constant-time requirements for cryptographic algorithms. Additionally, to counter power-based side-channel attacks, we adopt the masking technique proposed in [75] for the Authenticated Encryption with Associated Data (AEAD).

**Code.** Our source code is publicly available at https://github.com/whYBeKim/Crystals-Kyber-on-AVR

**Organization.** In Section 2, we review related work and examine the direction of PQC migration for 8-bit AVR. Section 3 introduces the necessary background knowledge. In Section 4, we propose the new KEM-MQTT protocol, and in Section 5, we introduce a novel modular reduction for Kyber (Signed LUT reduction) optimized for the 8-bit AVR environment. Section 6 presents a protocol-friendly Kyber implementation.

## 2 Related Works and Problem Statements

This section examines security protocols used in Wireless Sensor Networks (WSNs) (cf. Section 2.1) and reviews quantum-secure protocols currently under study for various embedded platforms (cf. Section 2.2). We then discuss key considerations for applying the PQC-KEM Kyber to WSNs and outline our approach to achieving quantum security on 8-bit AVR microcontrollers (cf. Sections 2.3 and 2.4). Finally, we briefly review recent trends in Kyber implementation on IoT devices (cf. Section 2.5).

## 2.1 Secure Protocols in WSNs

Advances in low-power technology have enabled WSNs to operate primarily on resource-constrained platforms such as microcontrollers, making them vulnerable to various attacks [41]. Due to the broadcast nature of wireless communication, WSNs are particularly exposed to threats such as eavesdropping and tampering, while their physical exposure increases risks like node capture and impersonation. Ensuring comprehensive security for microcontrollers remains a challenge. Over the past two decades, cryptographic techniques have evolved alongside improvements in sensor node performance. Initially, protocols such as IPSec and TLS were considered infeasible for sensor networks, leading to the development of lightweight alternatives like TinySec [41]. However, TinySec lacked mechanisms for non-repudiation and key establishment [51]. The proliferation of IoT services has expanded sensor node applications, increasing interest in scalable publish-subscribe models such as MQTT [31, 53].

Recently, Hamad et al. [31] analyzed MQTT's security features, yet most studies remain focused on conventional cryptographic schemes that are susceptible to quantum attacks [24, 50, 69].

## 2.2 WSNs in the Post-Quantum Era

As quantum security becomes increasingly critical, the migration of security protocols to PQC has emerged as a key research area. Recent studies have applied PQC to protocols such as IPSec [11], SSL/TLS [32], and SSH [79], while similar efforts have been made for lightweight protocols like MQTT. In 2020, Agus et al. [3] replaced RSA with NTRU (N-th degree truncated polynomial ring) in the MQTT-IoT protocol. The migration was successfully implemented on a Raspberry Pi, where NTRU outperformed RSA at the same security level. Schoffel et al. [69] benchmarked TLS handshake latency using NIST PQC Round 3 algorithms on MQTT, targeting lowpower Cortex-M4 sensor nodes. Additionally, Rampazzo and Henriques [66] evaluated PQC and hybrid cryptographic approaches within MQTT. Lukas Malina et al. [49] emphasized the importance of TLS in securing MQTT but noted its limitations in resourceconstrained environments requiring lower latency. Consequently, they proposed a PQC-based solution without TLS. These studies indicate that on Cortex-M/A series devices, PQC schemes exhibit performance levels comparable to Elliptic-Curve Cryptography (ECC)based schemes. However, most practical PQC migrations have been conducted on midrange or high-performance microcontrollers (e.g., 32-bit and 64-bit architectures) [2, 4, 14, 16, 33, 34, 43, 44, 73, 84]. In contrast, research on smaller sensor nodes, such as 8-bit and 16-bit devices [76], remains limited, with few reported implementations of PQC on 8-bit devices. As quantum computing advances, these smaller devices may become weak links systems, creating potential security vulnerabilities if the broader computing infrastructure transitions to PQC.

## 2.3 8-bit AVR Sensor Nodes

The 8-bit AVR is a modified Harvard architecture-based, reduced instruction set computing (RISC) single-chip microcontroller [7]. Its smaller register size, compared to other embedded processor families, makes it particularly suitable for cost-sensitive and lowpower applications. It is widely used in residential sensor-based products, such as thermostats, fire detectors, and glass break detection systems, and continues to play a significant role in the sensor node market [5]. Additionally, demand for 8-bit AVR microcontrollers is expected to grow due to their ability to reduce the cost of medical devices while maintaining reliable data acquisition [56]. The 8-bit AVR features a simple single-level pipeline structure and 32 general-purpose registers, each 8-bit in size. The six most significant registers—denoted as X[r26:r27], Y[r28:r29], and Z[r30:r31]-function as indirect address register pointers. These can access 16-bit memory addresses in pairs, with only the Z[r30:r31] pointer capable of accessing flash memory. A detailed description of the 8-bit AVR architecture and its instruction set is provided in Appendix A.

## 2.4 Embedding Kyber on AVR for WSNs

Low-power sensor nodes in WSNs typically integrate a single-core microcontroller with multiple communication and sensor modules

Table 1: Implementations of Public Key Schemes on AVR

| Algorithm  | Work                      | Speed[cc] | Stack[B] | AVR |

|------------|---------------------------|-----------|----------|-----|

| ECDH*      | [61]                      | 29,400 k  | -        | ✓   |

| Kyber-512  | Ref [40]                  | -         | 9,576    | X   |

| Kyber-512  | This Work<br>(based [16]) | 34,904 k  | 2,324    | ✓   |

| ECDSA*     | [36]                      | 77,779 k  | 1,642    | ✓   |

| Dilithium2 | [37]                      | 150,676 k | 12,751   | X   |

\*ECDH [61] uses curve P-256, and ECDSA [36] uses Ed25519

rather than employing System-on-Chip solutions. A representative example is the AVR-IoT WG Development board, which features an ATmega4808 core (6KB SRAM, 48KB Flash Memory) and various submodules [52]. While the board can utilize the WINC1510 communication module for TLS/SSL support, achieving quantum security requires moving beyond ECC-based cryptography. Specifically, implementing PQC schemes such as PQC-KEM and PQC-DSA in an AVR environment is necessary for authentication and key establishment.

One potential approach is building OpenSSL-based OQS-TLS on AVR. However, our experiments show that even with embedded options enabled, OpenSSL requires at least 16 KB of stack memory [59], which exceeds AVR's constraints. While introducing a PQC submodule similar to the ATECC608A is an option, ASIC development involves significant costs and time, making it impractical. Additionally, integrating an expensive PQC hardware module into a low-cost AVR platform is inefficient and unlikely to attract industry adoption. Instead, our goal is to implement PQC directly on the AVR core and conduct communication simulations based on this implementation.

Table 1 compares the performance of recent ECDH and ECDSA implementations on 8-bit AVR. A ✓ indicates successful implementation, while X denotes failure due to stack issues. Although [61] does not explicitly report the stack usage of ECDH, its smooth execution on an ATmega128 (4KB SRAM) suggests that P-256based ECDH is feasible. In contrast, ECDSA [36] requires 1,642 bytes of stack memory. More recently, Vincent et al. [37] simulated Dilithium2 on an 8-bit AVR using IAR AVR WorkBench with a 16 MB SRAM setting. Despite stack optimization, Dilithium 2's signature generation and verification require approximately 12 KB of SRAM, with its basic parameters (pk, sk, sig) consuming 6 KB. Given the total memory usage exceeding 18 KB, executing the full Dilithium stream on an 8-bit AVR is impractical. One alternative is storing the public key in flash memory while limiting operations to signature verification. However, as discussed in [37], Dilithium's reliance on 32-bit modular arithmetic makes it significantly slower on an 8-bit AVR compared to schemes using 16-bit modular arithmetic. Similarly, Falcon, which involves polynomial multiplications of degree 512/1024, is not an optimal choice for AVR.

Drawing from the KEMTLS methodology [71], we avoid PQC-DSA in 8-bit AVR environments, as it demands larger parameters, increased code size, and higher computational overhead compared to PQC-KEM. KEMTLS improves performance over standard TLS 1.3 by replacing PQC-DSA with PQC-KEM for authentication. In

this work, we apply KEMTLS to the MQTT protocol without relying on TLS/SSL. However, Kyber has not yet been implemented in an AVR environment. Our attempt to port Kyber's clean reference code [40] to the ATmega4808 failed due to excessive stack usage (approximately 10 KB). To address this, we implement Kyber-512 using memory optimization techniques proposed in [16], achieving a maximum stack usage of 2,324 bytes on the ATmega4808. However, as shown in Table 1, Kyber-512 is significantly slower than ECDH [61] at the same security level on an 8-bit AVR. Applying KEMTLS may further widen this performance gap. To mitigate this, we propose quantum-secure KEM-MQTT for AVR sensor nodes, demonstrating that Kyber can operate faster than ECDH without increasing stack requirements.

## 2.5 Kyber implementation on IoT Devices

Since Kyber's introduction in 2017, research on its optimization has intensified, Particularly following NIST's selection of Cortex-M4 for performance evaluation in the PQC competition [2, 4, 6, 16, 33, 64]. Kyber's core operation, polynomial-based matrix-vector multiplication, initially focused on reducing memory footprint and efficiently porting reference code to Cortex-M4. Thanks to extensive research, highly optimized Kyber implementations now exist [33]. Studies have also explored PQC implementations on Cortex-M0/M3 [1] and higher-tier architectures such as Cortex-A [14, 43, 44]. However, matrix-vector multiplication techniques differ across architectures, necessitating a tailored approach for 8-bit AVR.

Table 2: State-of-the-art implementation techniques for Kyber across Various Architectures

| Modular Arithmetic             | Platform          | AVR |

|--------------------------------|-------------------|-----|

| Solinas [83]                   | HW (FPGA)         | X   |

| Plantard [33, 34, 85]          | Cortex-M4, RISC-V | X   |

| Montgomery [73]                | AVX2, x86/64      | ×   |

| Barrett [14]                   | Cortex-A          | X   |

| Implementation Skills          | Platform          | AVR |

| Merging Layer [2, 4]           |                   | X   |

| CT-CT butterfly [2, 73]        |                   | X   |

| Streaming Coefficient [16]     | Almost all        | ✓   |

| Better Accumulation [2]        |                   | Δ   |

| Asymmetric Multiplication [14] |                   | Δ   |

✓: Suitable for AVR, X: Inefficient on AVR, △: Depends on board spec

Table 2 presents the state-of-the-art optimization techniques for Kyber implementations across various platforms. An  $\mspace{\times}$  indicates inefficiency on AVR, while a  $\mspace{\times}$  denotes suitability. Unlike modular arithmetic methods, implementation techniques listed in the second section of the table can be applied to most software platforms. A  $\mspace{\times}$  signifies that while a technique is applicable, it may increase stack usage, requiring caution. From a modular arithmetic perspective, we introduce a new reduction method (cf. Section 5), and from an implementation perspective, we propose a protocol-friendly methodology (cf. Section 6).

#### 3 Preliminaries

## 3.1 MOTT

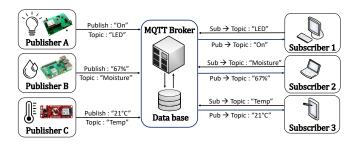

Figure 1: An example MQTT network

The MQTT architecture is based on a publish-subscribe model, involving three key entities: publisher, broker, and subscriber. The publisher, sometimes referred to as the client is typically a sensor node in IoT environments, while the broker acts as a gateway, tracking subscriptions and managing message distribution. The publisher sends sensor-generated data, such as temperature or heart rate, to the broker, which then forwards it to subscribers based on specified topics. While a single node can function as both a publisher and a subscriber, resource-constrained IoT devices often subscribe to only a few topics or none at all [31]. Figure 1 illustrates an example of MQTT interactions. Notably, pure MQTT lacks built-in security features. As discussed in Sections 2.2 and 2.1, research has proposed methods to achieve authentication, confidentiality, and integrity [24, 31, 50, 69]. Most security implementations rely on the TLS/SSL protocol stack.

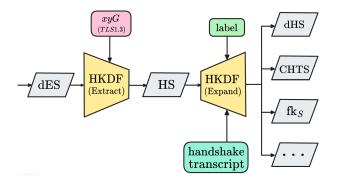

## 3.2 KEMTLS

| AVR(Client)                                                                                  |                      | Server                                                               |

|----------------------------------------------------------------------------------------------|----------------------|----------------------------------------------------------------------|

| $(pk_a, sk_a) \leftarrow \text{Keygen}$                                                      | $\xrightarrow{pk_a}$ | $static(Kyber_s): pk_s, sk_s$                                        |

| Q = 1, 70                                                                                    | $\leftarrow ct_a$    | $(ss_a, ct_a) \leftarrow Encaps(pk_a)$                               |

| $ss_a \leftarrow \text{Decaps}(ct_a, sk_a)$<br>$(ss_s, ct_s) \leftarrow \text{Encaps}(pk_s)$ | $\xrightarrow{ct_s}$ |                                                                      |

| $ss \leftarrow (ss_a  ss_s)$                                                                 |                      | $ss_s \leftarrow Decaps(ct_s, sk_s)$<br>$ss \leftarrow (ss_a  ss_s)$ |

|                                                                                              |                      |                                                                      |

Figure 2: High-level overview of the handshake phase on KEM-TLS, using Kyber for server authentication [28]

KEMTLS, based on TLS 1.3, employs a KEM for both key establishment and authentication. This approach enables unilaterally authenticated (server-side) key establishment without requiring additional round trips [71]. Unlike traditional TLS 1.3, KEMTLS

allows the client to send its first encrypted application data without caching or predistributing the server's public key, maintaining the same number of handshake round trips. A high-level overview of the KEMTLS handshake is shown in Figure 2, where the client is replaced by an AVR for illustration. KEMTLS consists of two KEMs: KEMe for ephemeral key exchange and KEMs for implicit authentication. Both can be instantiated using the same algorithm (in this case, Kyber). A recent benchmark study on KEMTLS in embedded environments [28] demonstrated that, on a Cortex-M4, KEMTLS reduced handshake time by up to 38% compared to TLS 1.3 while also reducing peak memory usage. Additionally, KEMTLS-PDK has been proposed for embedded devices with predistributed keys [72]. A complete outline of KEMTLS-PDK, where the client holds the server's static public key, is provided in Appendix D.

**Table 3: Kyber Parameter sets**

|            | Security | n   | $k, \ell$ | q    | pk[B] | sk[B] | ct[B] |

|------------|----------|-----|-----------|------|-------|-------|-------|

| Kyber-512  | 1        | 256 | 2         | 3329 | 800   | 1632  | 768   |

| Kyber-768  | 3        | 256 | 3         | 3329 | 1184  | 2400  | 1088  |

| Kyber-1024 | 5        | 256 | 4         | 3329 | 1568  | 3168  | 1568  |

## 3.3 Crystals-Kyber

Kyber is the only Key Encapsulation Mechanism (KEM) algorithm selected by NIST and its security is based on Module Learning With Errors (Module-LWE) problem. Since characteristic of Module-LWE-based Kyber, each element in a matrix and a vector is a polynomial over Ring  $R_q = \mathbb{Z}_q[X]/(X^n+1)$  where n = 256 and q = 3329. The public matrix **A** exhibits a size of  $\ell \times \ell$ , while the secret vector **s** and noise vector **e** each possess a size of  $\ell \times 1$ . For security levels 1, 3, and 5, the corresponding values of  $\ell$  are 2, 3, and 4, respectively. The polynomial in A has coefficients less than q, and the polynomials in s and e have very small coefficients. Table 3 shows parameter set of Kyber. Kyber's Public Key Encryption (PKE) consists of three operations: Key generation, Encryption, and Decryption, and Kyber-KEM utilizes Kyber-PKE with Fujisaki-Okamoto transform for providing IND-CCA2 security. Except for the random sampling based on hash function, the core operation of each Kyber-PKE algorithm is either matrix by vector multiplication  $(A \circ s)$  or vector by vector multiplication ( $\hat{\mathbf{s}}^T \circ \mathbf{u}$ ). For example, multiplication with a  $\ell \times \ell$  matrix and a  $\ell \times 1$  vector requires  $\ell^2$  polynomial multiplications (vector by vector multiplication requires  $\ell$  polynomial multiplications). The details of the Kyber description can be found in the Kyber specification document [9]. For the complete pseudocode structure of Kyber PKE, please refer to Algorithm 4, 3, and 5 in Appendix E. Please see Appendix F for the KEM algorithms. The core operation of Kyber, polynomial multiplication, is implemented using NTT. For a brief explanation of NTT, please refer to Appendix B.

## 3.4 Modular Arithmetic

Kyber's 16-bit polynomial elements result in 32-bit multiplications, necessitating reduction by q using nonconstant-time division operations. To mitigate timing-based side-channel attacks, efficient constant-time reduction methods are essential. The following subsections review existing modular reduction algorithms, both unsigned and signed, in lattice-based cryptography.

3.4.1 Unsigned Modular Reduction Methods. Before NIST's PQC competition, various lattice-based cryptosystems were implemented on 8-bit AVR MCUs [48, 74]. Liu et al. [48] introduced an efficient modular reduction method for NTT-based polynomial multiplication, employing a Shift-Add-Multiply-Subtract-Subtract (SAMS2) technique for approximate reduction. This method estimates  $\lfloor c/q \rfloor$  using shifts and arithmetic operations, making it suitable for integer division with specific q values. However, it may require an additional subtraction for final reduction due to its unsigned range. Seo et al. [74] enhanced this approach by introducing a Lookup-Table (LUT) method that replaces quotient computation with predefined remainders. Unlike cache-based methods, this approach is resistant to cache-timing attacks on 8-bit AVR MCUs, which lack cache memory (cf. Figure 3).

Figure 3: Unsigned LUT reduction for q = 7681, blue box means each step, step 1,2: LUT access; step 3: addition; step 4,5: shifting; step 6: modulo; step 7: addition and subtraction [74]

3.4.2 Modular Reduction Methods used in Kyber. As efficient and constant-time reduction algorithms, Montgomery method [55] and Barrett method [13] have been widely used for efficient modular reduction in public key cryptosystems. In addition, recently an improved Plantard reduction has been proposed and applied to Kyber [62]. The algorithms for each method can be found in the Appendix H. In the context of lattice-based cryptography using small prime q, the signed Montgomery method (Algorithm 12) and signed Barrett method (Algorithm 13) were proposed [73] and have been applied to the implementations of Kyber and Dilithium. Signed reduction is denoted by  $\operatorname{mod}^{\pm} q$  and  $c \operatorname{mod}^{\pm} q$  reduces into  $\left(-\frac{q}{2}, \frac{q}{2}\right)$ . The core principle of each method is replacing division by q with shift operations which can be efficiently computed on computing devices. The unsigned LUT-based reduction method from [74] has been considered as being the fastest on AVR MCUs. However, the underlying q = 7681 in their implementation is different from the q = 3329 in Kyber. Furthermore, after Seo et al.'s method [74], it has been shown that signed versions of several reduction methods [2, 4, 73] contribute to much-improved performance of Kyber on several devices on 32-bit ARM, 64-bit ARMv8, and x86-64-bit CPUs. Thus, it is necessary to fill this research gap by answering the questions: which reduction method among the unsigned LUT-based method and signed reduction methods gives the best performance on 8-bit AVR MCUs and whether there is a new method providing better performance compared with existing methods.

## 4 Proposed Secure MQTT Protocol on AVR

## 4.1 Security Goal

In MQTT, communication occurs among three entities, but recent research on PQC-based MQTT has primarily focused on higherperformance IoT devices, such as 64-bit Raspberry Pi and Apple Silicon, rather than resource-constrained 8-bit AVR [49, 68]. The study in [68] proposed a theoretical application of KEMTLS but did not conduct practical experiments or address migration challenges such as certificate management and authentication. Meanwhile, [49] explored the migration of certificates to PQC but focused on scenarios involving high-performance IoT devices, where a single device could act as both a publisher and a subscriber. However, resourceconstrained AVR sensor nodes are typically deployed in physically insecure environments in large numbers, often ranging from tens to hundreds. These nodes generally function solely as publishers, with the broker managing them [41, 42]. The study in [49] employed PQC-DSA for publisher authentication, but as discussed in Section 2.4, PQC-DSA is impractical for AVR environments. Therefore, we simplify the AVR-based scenario based on several assumptions and apply the KEMTLS methodology as follows:

- Only Publisher: The AVR device functions exclusively as a publisher and communicates only with the broker.

- Broker Authentication: KEMTLS provides implicit server-toclient authentication when the client sends its first application data. Similarly, we achieve implicit authentication for the broker using KEM, while explicit authentication is established upon receiving the key confirmation message.

- Publisher Authentication: TLS typically performs only serverside authentication. To prevent sensor node impersonation by malicious attackers, explicit authentication for the publisher is necessary without relying on PQC-DSA. By applying the KEMTLS methodology, we achieve authentication in MQTT using only KEM, ensuring mutual authentication.

- Confidentiality and Integrity: Published data and handshake messages are encrypted using Authenticated Encryption (AE). which ensures both confidentiality and integrity. Additionally, we allow the transmission of associated data, including the publisher's ID (id<sub>P</sub>) and topic (T), which are protected using the Authenticated Encryption with Associated Data (AEAD) algorithm. While the associated data itself is not encrypted, its integrity is guaranteed.

- No Certificates: In TLS 1.3, certificates verify the server's long-term key, but when embedded devices communicate with a limited set of preknown servers, predistributing the server's static key is a viable alternative. This is known as the Predistributed Key (PDK) or cached-key scenario [70]. Certificates can also be distributed via DNS [38], though this is suboptimal for MQTT environments. Given that AVR-based sensor nodes communicate exclusively with the broker, they can store the broker's public key (pk<sub>B</sub>) in flash memory before deployment. Similarly, the broker is assumed to know the AVR-based sensor node's public keys (pk<sub>P</sub>). In this model, the broker is considered a semitrusted entity.

In summary, our goal is to apply the KEMTLS methodology to achieve confidentiality, integrity, and mutual authentication. The keys exchanged during the handshake must be indistinguishable

Figure 4: Sketch of KEM-MQTT with proactive client authentication

$$\begin{array}{c|c} \textbf{Publisher (AVR)} & \textbf{Broker} \\ \\ \textbf{static (KEM$_P$) pk$_P$, sk$_P$, id$_P$ static (KEM$_B$) pk$_B$, sk$_B$ knows pk$_B$ knows id$_P$ and H(pk$_P$) \\ \hline (pk$_e$, sk$_e$) \leftarrow KEM$_e$.Keygen() \\ (ss$_B$, ct$_B$) \leftarrow KEM$_B$.Encaps(pk$_B$) \\ \hline & K$_B$ \leftarrow KDF(ss$_B$) \\ pk$_e$, ct$_B$, AEAD$_K$_B$ (id$_P$||pk$_P$) \\ \hline & ss$_B$ \leftarrow KEM$_B$.Decaps(ct$_B$, sk$_B$) \\ (ss$_e$, ct$_e$) \leftarrow KEM$_e$.Encaps(pk$_e$) \\ (ss$_P$, ct$_P$) \leftarrow KEM$_P$.Encaps(pk$_P$) \\ \hline & ct$_e$ \\ \hline & ss$_e$ \leftarrow KEM$_e$.Decaps(ct$_e$, sk$_e$) \\ \hline & K$_1$ \leftarrow KDF(ss$_e$||ss$_B$) \\ \hline & AEAD$_{K$_2$}$(ct$_P$, sk$_P$) \\ \hline & K$_2$, K$_2$', K$_2$''' \leftarrow KDF(ss$_e$||ss$_B||ss$_P$) \\ \hline & AEAD$_{K$_2$''}$ (key confirmation same as TLS 1.3) \\ \hline & AEAD$_{K$_2$'''}$ (timestamp $t$ || Topic $T$ || data $d$) \\ \hline \end{array}$$

from random keys, ensuring forward secrecy—even if long-term keys are compromised; deriving secret keys. The assumption that the publisher and broker know each other's long-term keys is reasonable in a PDK scenario, as the broker must register each sensor node before deployment. If a new publisher is introduced with higher computational capabilities than an AVR, standard certificate-based public-key authentication can be employed [72]. Therefore, in our scenario, the AVR does not need to verify pk<sub>B</sub>'s certificate, nor does the broker need to send it. Instead, the broker must reliably identify the public key of each sensor node.

## 4.2 Quantum Secure KEM-MQTT Protocol

Figure 4 illustrates the overall KEM-MQTT process. KEM-MQTT is based on KEMTLS-PDK [72], a variant of KEMTLS that leverages the PDK scenario. KEMTLS-PDK reduces the amount of transmitted data during the handshake compared to TLS 1.3. Similarly, KEM-MQTT explicitly authenticates both the publisher and broker without requiring additional round trips. While the TLS-PDK scenario allows the client to bypass server certificate validation using cached

information [70], this approach was not widely adopted prequantum due to the relatively short length of classical certificates [82]. However, in the postquantum setting, skipping certificate validation is highly advantageous for AVR-based devices, particularly given the impracticality of PQC-DSA. As a result, in KEM-MQTT, the broker does not send  $pk_B$  to the AVR; Instead, the publisher sends its public key  $(pk_P)$  to the broker.

From a postquantum certificate perspective, a Dilithium2 signature requires approximately 2 KB, while a Kyber-512 public key is 800 bytes. This means the broker would require at least 3 KB of buffer space per node. If certificates were further expanded, memory requirements would increase significantly. In a scenario where hundreds of AVR-based wildfire detection sensors are deployed in remote areas, requiring the broker to store all sensor nodes' certificates would impose a significant burden. To address this, we propose that the broker stores a 32 bytes hash of the public key. This provides an explicit authentication mechanism for  $pk_P$ . Since the broker already knows  $id_P$  and  $pk_P$  prior to sensor deployment, storing all public keys is unnecessary. Instead, the broker can differentiate sensor nodes using their public-key hashes, effectively replacing certificates with hash values.

In KEM-MQTT, the publisher securely transmits its public key  $(pk_P)$  and identifier  $(id_P)$  to the broker by encapsulating it with  $pk_B$  and using the shared secret. This process is analogous to a client sending authentication information to a server during a TLS 1.3 handshake. KEM-MQTT achieves mutual authentication in a single round trip. In TLS 1.3, the server is authenticated upon receiving the first message from the client. Similarly, in KEM-MQTT, the broker is explicitly authenticated through key confirmation information included in the first message, completing authentication after one round trip.

Additionally, KEM-MQTT allows the broker (server) to send data to the publisher (client) immediately after mutual authentication, as in TLS 1.3 and KEMTLS-PDK. Since KEM-MQTT is based on the KEMTLS-PDK model, it inherits critical security properties such as forward secrecy, explicit authentication, and key-use guarantees, all of which can be formally proven using the KEMTLS-PDK Multistage-secure proof methodology [72]. The detailed security proofs of KEM-MQTT, including reduction-based security proofs and Tamarin Prover verification [72], are left for future work.

## 5 Proposed Signed LUT Reduction for Kyber

This section presents optimization strategies for Kyber on an 8-bit AVR. Our approach focuses on reducing both multiplication and addition results. We implemented both of our proposed methods and existing ones in AVR assembly and found that our methods achieved the best performance.

## 5.1 Design of Signed LUT Reduction

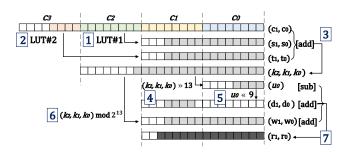

The proposed Signed LUT reduction (*SLR*) method for modulus q = 3329 is described in Algorithm 1, with a high-level overview shown in Figure 5. In this method,  $c_3$ ,  $c_2$ , and the upper 4-bits of  $c_1$  are reduced to fit within the lower 12-bit of c. Algorithm1 operates on a 28-bit input range ( $c \in (-q2^{15}, q2^{15})$ ), corresponding to the signed Montgomery method [73], and produces a 14-bit output ( $r \in (-q, 2^{13})$ ), matching the output size of the unsigned

LUT reduction method [74]. Instead of fine-tuning the input and output bit ranges, we focus on accelerating reduction with minimal instructions. Our experiments show that generating a 12-bit output incurs a higher computational cost than a 14-bit output. On 8-bit AVR MCUs, input data c is represented as four 8-bit words. However, since  $c \in (-q2^{15}, q2^{15})$ , the actual data is stored within 28-bits, with the upper 4-bits serving as a sign-bit extension.

We introduce two LookUp-Tables (LUT#1 and LUT#2), where each LUT produces a signed 12-bit output from an 8-bit signed or unsigned input. We build LUT#1 for reference to  $(c_2 \cdot 2^{16}) \mod^{\pm} q \in (-\frac{q}{2}, \frac{q}{2})$  (step 1 of Figure 5). We construct the input data to LUT#2 by combining the lower 4-bit of  $c_3$  and the upper 4-bits of  $c_1$  (step 2). After that, we build LUT#2 for reference to  $((c_3[3]|\cdots||c_3[0])_{sb}\cdot 2^{24}+(c_{1[7]}||\cdots||c_{1[4]})_b\cdot 2^{12}) \mod^{\pm} q \in (-\frac{q}{2}, \frac{q}{2})$  (step 3). These two LUTs can be precomputed because the values in them are constant. The SLR involves division into word units but does not require bit shift, thereby eliminating the need for additional costs. We considered various methods for applying LUTs and, after careful calculation of the output range and estimation of operational costs, confirmed that the approach depicted in Figure 5 is the most optimal. The proof of the correctness of the SLR method is as follows. Since the input data is less than 32-bit, experimental verification does not take long to verify all cases with a personal laptop.

#### Algorithm 1 Signed LUT reduction for Kyber

Input:  $c = c_3 \cdot 2^{24} + c_2 \cdot 2^{16} + c_1 \cdot 2^8 + c_0$ , for  $c \in (-q2^{15}, q2^{15})$ , with  $c_i := (c_{i[7]} \parallel c_{i[6]} \parallel \cdots \parallel |c_{i[0]})_{b(sb)}$ ,  $i \in [0, 3]$  (sb means signed binary representation), all outputs of LUT#1 and LUT#2 in  $(-\frac{q}{2}, \frac{q}{2})$

**Output:**  $r \equiv c \mod^{\pm} q$ , where  $r \in (-q, 2^{13})$

1:

$$u = (c_2 \cdot 2^{16}) \mod^{\pm} q$$

$\Rightarrow u = LUT#1$

2:  $v = ((c_{3[3]}||\cdots||c_{3[0]})_{sb} \cdot 2^{24}$

$+(c_{1[7]}||\cdots||c_{1[4]})_b \cdot 2^{12})) \mod^{\pm} q$   $\Rightarrow v = LUT#2$

3:  $r = u + v + (c_{1[3]}||\cdots||c_{1[0]})_b \cdot 2^8 + c_0$

4: return r

Figure 5: Proposed signed LUT reduction for q = 3329, step 1 and 3: accessing LUT; step 2: combining parts to be reduced; step 4: accumulating remainders

**Theorem.** Let q = 3329 be an odd modulus of Kyber, then Algorithm 1 is correct for input data  $c = c_3 \cdot 2^{24} + c_2 \cdot 2^{16} + c_1 \cdot 2^8 + c_0$ , where  $c \in (-q2^{15}, q2^{15})$ .

PROOF OF THEOREM. To prove the correctness of Algorithm 1, we need to show that there is an equivalence relation between r and c on modulus q ( $r \equiv c \mod^{\pm} q$ ); and, to show that the final result r is in  $(-q, 2^{13})$ .

First, using the linearity of modular arithmetic, we prove the modulo congruence over q. After that, we prove the range of r is well fit through signed representation.

(1) We are going to prove modulo congruence by explaining the generation of LUT#1 and LUT#2. First, *c* can be expressed in four words (8-bit) as follows:

$$c \equiv (c_3 \cdot 2^{24} + c_2 \cdot 2^{16} + c_1 \cdot 2^8 + c_0) \mod^{\pm} q$$

$$c \equiv (c_3 \cdot 2^{24} + c_1 \cdot 2^8 + c_0 + \underbrace{(c_2 \cdot 2^{16}) \mod^{\pm} q}_{u}) \mod^{\pm} q$$

$$c \equiv (c_3 \cdot 2^{24} + c_1 \cdot 2^8 + c_0 + \underbrace{\text{LUT#1}}_{u}) \mod^{\pm} q$$

(5)

As shown in first step of Algorithm 1,  $u = c_2 \cdot 2^{16} \mod^{\pm} q$  can be replaced by LUT#1. Therefore, we can show  $c \equiv (c_3 \cdot 2^{24} + c_1 \cdot 2^8 + c_0 + \text{LUT#1}) \mod^{\pm} q$ .

(2) For  $c = c_3 \cdot 2^{24} + c_2 \cdot 2^{16} + c_1 \cdot 2^8 + c_0$ , Let  $c_i$  be  $(c_{i[7]} \parallel c_{i[6]} \parallel \cdots \parallel c_{i[0]})_{(sb)}$  with  $i \in [0,3]$ , here, sb means signed binary representation. Since  $c \in (-q2^{15},q2^{15})$ , c can actually be represented as 28-bit with signed representation. Therefore, the  $27^{th}$  bit from LSB (Least Significant Bit) of c is an extended sign-bit. Finally, Equation 5 can be re-written as follows:

$$c \equiv ((c_{3[3]}||\cdots||c_{3[0]})_{sb} \cdot 2^{24}$$

+  $c_1 \cdot 2^8 + c_0 + \underline{\text{LUT}} \text{mod } ^{\pm} q$  (6)

Please note that  $(c_{3[3]}||\cdots||c_{3[0]})_{sb}$  and  $c_1$  can be represented as  $c_1 = (c_{1[7]}||\cdots||c_{1[4]})_b \cdot 2^4 + (c_{1[3]}||\cdots||c_{1[0]})_b$ . Let LUT#2 be  $((c_{3[3]}||\cdots||c_{3[0]})_{sb} \cdot 2^{24} + (c_{1[7]}||\cdots||c_{1[4]})_b \cdot 2^{12}))$  mod<sup>±</sup>q. Then, referring to v in step 2 of Algorithm 1, Equation 6 can be simply derived as follows:

$$r \equiv c \equiv (\underline{\text{LUT#2}} + \underline{\text{LUT#1}}_{u} + (c_{1[3]}||\cdots||c_{1[0]})_{b} \cdot 2^{8} + c_{0}) \text{ mod } ^{\pm}q$$

(7)

Therefore, for signed input  $c \in (-q2^{15}, q2^{15})$ , it is equivalent to  $r \equiv c \mod^{\pm} q$ .

(3) Since u and v are signed integers, LUT#1 and LUT#2 are in  $(-\frac{q}{2},\frac{q}{2})$ . Note that each LUT returns a 12-bit reference result value for an 8-bit input. Because  $(c_{1[3]}||\cdots||c_{1[0]})_b\cdot 2^8+c_0)$  is an unsigned integer, so the range is greater than 0 and less than  $2^{12}$ . Putting this together, we show that the ranges of input and output are correct as follows:

Since

$$-\frac{q}{2} < \underline{\text{LUT\#1}}, \ \underline{\text{LUT\#2}} < \frac{q}{2} \text{ and}$$

$$0 \le (c_{1[3]}||\cdots||c_{1[0]})_b \cdot 2^8 + c_0 < 2^{12},$$

we have  $-q < r < 2^{12} + q < 2^{13}$ . (8)

## 5.2 Design of Signed Small LUT Reduction

## Algorithm 2 Signed Small LUT reduction for Kyber

```

Input: The signed integer a = a_1 \cdot 2^8 + a_0, for a \in [-2^{15}, 2^{15})

Output: r \equiv a \mod^{\pm} q, where r \in (-\frac{q}{2}, 2^{11})

1: u = (a_1 \cdot 2^8) \mod^{\pm} q \blacktriangleright \text{LUT#3}, u \in (-\frac{q}{2}, \frac{q}{2})

2: return r = u + a_0

```

We introduce a fast method for reducing 16-bit inputs, termed signed small LUT reduction (SSLR, cf. Algorithm 2). On an 8-bit AVR environment, a 16-bit input (a) is represented as two bytes. Using a LUT (LUT#3), we first reduce the upper byte a  $(a_1 \cdot 2^8)$  to the range  $(-\frac{q}{2}, \frac{q}{2})$ . Then, we add the lower byte a  $(a_0)$  to obtain the output r, which remains within 12-bit value due to the bound  $(\frac{q}{2} + 255) < 2^{11}$ . The correctness of SSLR follows directly from the same reasoning used in the SLR case. Although SSLR produces a slightly wider range of output values compared to Barrett reduction, it maintains the same input and output bit sizes. This minor increase in range does not necessitate additional reductions in the overall Kyber implementation.

While the proposed SLR and SSLR methods notably improve performance over existing signed reduction methods, they rely on lookup tables, which could be seen as a drawback. However, this issue is mitigated as follows: Our method requires additional LUTs containing double-word values—SLR uses two LUTs, while SSLR requires one. Each LUT occupies 0.5 KB (16-bit  $\times$  256), amounting to a total memory of 1.5 KB. These LUTs are stored in flash memory, as 8-bit AVR MCUs typically have ample flash memory (48 KB) relative to their RAM size (6 KB). Storing the LUTs in flash consumes only 3.15% of available flash memory. If all LUTs were allocated to the stack, SLR and SSLR would achieve execution times of 23 and 9 cycles, respectively. These configurations are particularly relevant for specific security levels or when additional SRAM is installed on the AVR board. Detailed memory placement strategies for LUTs are discussed in Section 6.

#### 5.3 Comparison to Existing Reduction Methods

Table 4 presents the cycle counts for various modular reduction methods on an 8-bit AVR device. For a fair comparison, we implemented all existing reduction methods using handwritten AVR assembly, and minimizing unnecessary operations. Appendix G provides the AVR code for *SLR* and *SSLR*. Our *SLR* and *SSLR* approaches outperform all previous methods proposed for Kyber. While our methods slightly expand the output range compared to conventional arithmetic, no additional reductions are required within Kyber's implementation.

5.3.1 Unsigned Arithmetic. The unsigned LUT reduction for modulus 7681, which is 13-bit, utilizes the  $2^{13} \equiv 2^9 - 1 \mod 7681$  to output a reduced result of 14-bit. However, Kyber's modulus q = 3329 is represented by summing consecutive powers of  $2 (q = 2^{12} - 2^9 - 2^8 + 1)$ . Therefore, rather than using the linearity of the modulus to narrow the output range, it is more effective to design the signed LUT reduction with only simple operations to increase the speed. With a simplified approach that only utilizes LUT references and accumulative operations, our *SLR* achieves huge performance improvement

(27 cycles compared to 40 cycles of unsigned LUT reduction) while preserving the same size of input and output as unsigned LUT reduction. Note that it is required to reduce intermediate results when computing NTT conversion (or inverse NTT conversion) consisting of 7 layers since the output of LUT methods is 14-bit. The method of Seo et al. [74] used a modular addition/subtraction-based approach, which is costly. In the case of our approach using signed representation, this process can be efficiently handled.

Table 4: Cycle counts for modular reduction on 8-bit AVR

| Variant   | Type     | Modular Arithmetic               | cycle count |

|-----------|----------|----------------------------------|-------------|

|           | Unsigned | Solinas [83]                     | 77          |

|           | Signed   | Plantard [33]                    | 56          |

| 32-bit    | Unsigned | LookUp-Table [74]                | 40          |

| reduction | Signed   | Montgomery [73]                  | 32          |

|           | Signed   | LookUp-Table (SLR) <sup>†</sup>  | 27          |

|           | Signed   | LookUp-Table (SLR) <sup>‡</sup>  | 23          |

| 16-bit    | Signed   | Barrett [73]                     | 33          |

| reduction | Signed   | LookUp-Table (SSLR) <sup>†</sup> | 11          |

| reduction | Signed   | LookUp-Table (SSLR) <sup>‡</sup> | 9           |

<sup>†:</sup> placing LUTs in flash memory, ‡: placing LUTs in stack

5.3.2 Signed Arithmetic. The existing signed methods have been tailored to ARM-based MCUs providing plenty of powerful instructions such as multiply-and-accumulate, halfwords multiply, doubling multiply, and so on. Since the instruction set of 8-bit AVR is much simpler than that of 32-bit/64-bit ARM-based MCUs, the existing signed methods require an increased number of instructions when implemented on 8-bit AVR. For example, 16-bit signed multiplication requires 17 clock cycles which are computed just 1 clock cycle on ARM-based MCUs. Furthermore, there are no multiply-andaccumulate-like instructions on 8-bit AVR MCUs. There is another limitation that makes existing signed reduction methods inefficient on 8-bit AVR. Also, in order to perform signed multiplication in AVR, the upper byte of the 16-bit coefficient needs to be stored in the 16th register or higher, and the multiplication result is output in [r0:r1]. In the case of signed Montgomery and signed Barrett methods, they are related to multiplication using additional constants q and  $q^{-1}$ , which require additional data movement between registers. In the case of the signed Plantard method, it requires 32-bit × 16-bit multiplication, which results in inefficient execution in 8-bit AVR MCUs. Our proposed SLR does not require any signed multiplication, but utilizes addition, bit-wise operation, and load instructions, which makes it more efficient than the existing signed reduction methods. Typically, Barrett reduction is used when reducing 16-bit operation in Kyber. However, as discussed from [33], since Barrett reduction requires v bit-shift operation where v is not a multiple of the word size (8-bit), it is more inefficient than Plantard method. Furthermore, signed Barrett reduction requires two 16-bit signed multiplication which is inefficient. Our SSLR replaces the use of signed Barrett reduction with efficient LUT-based operations.

## 6 Proposed Protocol-friendly Implementation6.1 Placing LUTs in Stack (Option)

In previous research, various methodologies were discussed to reduce stack usage during signature generation in the Dilithium [15, 29]. Unlike Dilithium [8], Kyber does not require consideration of vector regeneration since it does not have a rejection-loop. Consequently, by streaming the public matrix A and error e as proposed in [16], each KEM API can be operated sufficiently within 8KB SRAM. From a more practical standpoint, we opt for the strategy of placing 1.5KB of LUTs on the stack implementing Kyber-512. Even with an additional 1.5KB of stack based on Kyber-512, the pk (800 bytes), sk (1,632 bytes), ct (768 bytes), and ss (32 bytes) can be maintained in 8KB SRAM. Analogous to the strategy of pre-hashing the public key, in the case of simple connections where the broker's public key is pre-loaded into flash memory, this can be more smoothly applied. By positioning the LUTs on the stack, the 1pm instruction can be converted into an 1d instruction, resulting in a one-cycle benefit. Unlike Asymmetric Multiplication [14], where the stack usage varies by security level, the same amount of stack usage can be maintained at all security levels, allowing for a more flexible selection depending on the various protocol. Finally, Placing LUT on stack, SLR and SSLR can be implemented in 23 cycles and 9 cycles on AVR environment, respectively.

## 6.2 Using Pre-hashed Public Key

Assuming that  $\mathsf{pk}_B$  is known, the hash value of  $\mathsf{pk}_B$  can be stored in flash memory. This hashed public key is 32 bytes, allowing the process of hashing the broker's public key in Kyber.CCAKEM Encaps (cf. Algorithm 7) to be skipped. Specifically, Line 2 of Algorithm 7,  $(\overline{K},r) := \mathsf{G}(m||\mathsf{H}(pk))$ , is accelerated. This strategy can be directly applied to our KEM-MQTT.

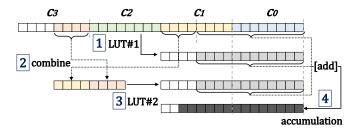

## 6.3 High-Speed Implementation

In general, speed and memory are in a trade-off relationship. Therefore, we chose not to adopt methods from state-of-the-art implementations, such as storing repeated calculations (Asymmetric multiplication [14]) or computing accumulations in larger buffers (Better Accumulation [2]). Instead, we focused on optimizing for performance by leveraging the characteristics of AVR. The following three implementation strategies accelerate Kyber's entire scheme without using additional stack memory.

First, while modular multiplication on Cortex-M4 requires 2 cycles, our *SLR* on AVR takes 23 cycles, despite being the fastest method available. To improve this, we introduced the Karatsuba method in point-wise multiplication, reducing one multiplication (17 cycles) and replacing it with cheaper addition/subtraction operations (2 cycles).

Second, we did not apply the CT butterfly to iNTT as done in [2, 14, 33]. The offset distance in AVR is limited to 32 bytes, and using the CT butterfly would introduce complex offset calculations for the twiddle-factor. Additionally, it would require an extra 1KB for storing the twiddle-factor for ring-twisting. Through extensive handwritten assembly, we confirmed that GS butterfly performs better. Similar to montgomery reduction, we use *SSLR* to call coefficient reductions only in two layers of iNTT.

Third, since the 1dd instruction has a maximum offset displacement of 64, we aligned the lower byte address of polynomials to 0x00 (attribute((aligned(256))) to allow access to up to 32 coefficients from the starting address. Without this alignment, additional instructions are required to handle the 16-bit address calculations within the NTT loop. For example, accessing data beyond 64 bytes would require the adc instruction for offset calculation. Additionally, we reduced one offset calculation per loop by considering that one of the butterfly input addresses could serve as the input address for the next butterfly within the inner NTT loop. We call this approach the crossed-butterfly (code in Appendix I).

## 6.4 Low-Memory Implementation

The reference code of Kyber-512 and Kyber-1024 respectively require approximately 10KB and 20KB of stack memory [9]. While implementations on various AVR-based boards are feasible at shortterm security levels, memory optimization becomes essential when considering mid-to-long-term security levels and real-world protocol scenarios. We apply the streaming approach for Kyber, as proposed in [16], to our implementation to its fullest extent. This method processes the public matrix A, required in the KeyGen, En-Caps, and DeCaps processes, via streaming without pre-allocating stack space. This approach is feasible under the assumption that the public matrix A already exists in the NTT domain. However, since the secret vector s requires NTT operations, at least one polynomial space is necessary. Consequently, the actual computation proceeds using only two polynomials, considering the space for accumulation. This approach allows all security levels of Kyber to utilize approximately 3KB of stack only. Additionally, our methodology enables flexible storage of LUTs in the stack and flash memory, depending on the board. Fundamentally, flash memory, typically sized in the tens of KB, is not a major concern in AVR.

## 6.5 Secure Implementation

Constant-time implementation is essential for defeating timing attack, a kind of side channel analysis using timing leakage [26]. Particularly, small sensor nodes can be physically captured and analyzed with side channel analysis. To prevent timing leakage, it needs to eliminate conditional branches and memory accesses depending on secret information. In our implementation approach, we convert all branching statements to execute in constant time. We meticulously examine the compilation results of each algorithm, manually identifying and addressing any branches in the assembler code. Following the method proposed in [80], we rigorously inspect and rectify areas where cycle fluctuations may occur. Regarding cachetiming attacks, a kind of enhanced timing attack using sophisticated microarchitectural cache hierarchy and operations of the target device [26], AVR devices, which operate in a cache-less environment, are not affected. Therefore, our approach, which employs LUT, is applicable without risk. From a power analysis countermeasure perspective, we refer to the AES-GCM implementation methodology with 128-bit security in [75] for countering power-based side-channel attacks. Unfortunately, the implementation in [75] is not open-sourced, so we implement it with handwritten assembly and apply it with the AEAD algorithm.

## 7 Experimental Results

## 7.1 Benchmarking Setup

We benchmarked the implementation using Microchip Studio. For Kyber-512, the target device was the ATmega4808, which has 6KB of RAM and 48KB of flash memory. Performance measurements for Kyber-768 and Kyber-1024 were conducted on the ATmega1280p, which has 8KB of SRAM. Although each API is implemented within 3KB of memory, the ATmega4808 lacks sufficient stack space to store essential parameters. The code was compiled using avr-gcc, provided by Microchip Studio, with the -03 optimization flag. The key schedule for KEM-MQTT follows the same structure as TLS 1.3, with one minor modification: we reuse the SHA-3 function used in Kyber and implement it as HKDF. To verify correctness, we experimentally re-evaluated the mathematical proof of the signed (Small) LUT reduction presented in Section 5.1. Additionally, we validated the correctness of our Kyber implementation using the Known Answer Test (KAT) from the NIST Round 3 submission (https://github.com/pq-crystals/kyber/tree/main/ref/nistkat).

#### 7.2 Performance Result of NTT/iNTT

The performance analysis of the components of the NTT-based polynomial multiplication, which is the core operation of Kyber, is presented in Table 5. Through the high-speed performance of SLR and SSLR, along with register scheduling and offset operations optimized for the characteristics of 8-bit AVR, we achieved performance improvements in both NTT and iNTT. Additionally, the application of SLR and Karatsuba multiplication contributed to the enhancement of basemul performance. Finally, compared to the naively ported implementation based on [16], our highly optimized implementation shows performance improvements of 98 (111)%, 67 (71)%, and 106 (120)% in NTT, basemul, and iNTT, respectively, when LUT is placed in flash memory (stack).

Table 5: Cycle counts for NTT/iNTT and single basemul

| Implementation             | NTT     | basemul | iNTT     |

|----------------------------|---------|---------|----------|

| This Work                  | 58,364  | 319     | 67,792   |

| (Signed LUT <sup>‡</sup> ) | (+111%) | (+71%)  | (+120%)  |

| This Work                  | 62,204  | 328     | 72,398   |

| (Signed LUT <sup>†</sup> ) | (+98%)  | (+67%)  | (+106%)  |

| This Work                  | 123,363 | 547     | 149,4778 |

| (based [16])               | (-)     | (-)     | (-)      |

<sup>†:</sup> placing LUTs in flash memory, ‡: placing LUTs in stack

## 7.3 Performance Result of Kyber

Table 8 shows the cycle counts and stack usage of the Kyber implementation in an 8-bit AVR environment. The strategy of placing the LUT in the stack ( $\diamond$ ), considering the board specifications, is applied only to Kyber-512. Through the *SLR* and *SSLR* techniques proposed in Section 3, and the protocol-friendly implementation methods proposed in Section 5, Kyber is optimized to the limit in the AVR environment. Compared to the naive implementation based on [15], we accelerated the Keygen, Encapsulation, and Decapsulation processes of Kyber by more than 70% across all security

levels (marked with  $\star \dagger$ ). By pre-hashing and storing the broker's public key and placing the LUT in the stack (marked with  $\star \diamond \ddagger$ ), Kyber-512 achieves performance improvements of 82%, 101%, and 86% in Keygen, Encapsulation, and Decapsulation, respectively.

Table 6: Comparison of Key establishment performance between Ephemeral ECDH and Kyber on 8-bit AVR MCUs, 1,000 cc is denoted by k and s means a second.

| Work   | Security              | $k \cdot P$ | $l \cdot Q$ | ECDH(cc)                   | ECDH(s)         |

|--------|-----------------------|-------------|-------------|----------------------------|-----------------|

| [81]   | GF(p), 160            | 9,920k      | 10,80k      | 20,720k                    | 2.81            |

| [46]   | GF(p), 160            | 15,100k     | 16,960k     | 32,060k                    | 4.35            |

| [47]   | GF(p), 192            | 3,460k      | 8,620k      | 12,080k                    | 1.63            |

| [30]   | GF(p), 224            | n/a         | 17,520k     | $24,550 \mathrm{k}^\oplus$ | 3.33⊕           |

| [86]   | GF(p), 256            | n/a         | 25,380k     | 35,560k <sup>⊕</sup>       | 4.82⊕           |

| [61]   | GF(p), 256            | n/a         | 20,980k     | 29,400 $k$ <sup>⊕</sup>    | $3.98^{\oplus}$ |

| var    | riant Ky              | ber-512(s)  | Kyber-7     | 68(s) Kybe                 | er-1024(s)      |

| This   | (★ ◊ ‡)               | 2.49        | -           |                            | -               |

| Th     | nis                   | -           | 3.87 (★     | ♦†)                        | 02 (★†)         |

| This [ | [16] ( <del>*</del> ) | 4.73        | 7.30        | )                          | 11.14           |

★, ⋄, †, and ‡: same as Table 8, ⊕: a roughly measured

## 7.4 Performance Comparison with ECDH

Table 6 presents a comparison between ECDH and Kyber. With the sophisticated field arithmetic approach proposed in [47], optimization research for scalar multiplication implementations began in earnest. Ephemeral ECDH is implemented on the NIST Curve using the window method and requires performing scalar multiplications for both the fixed point P and random point Q. The research in [86] and [61] does not provide performance results for Ephemeral ECDH; therefore, we estimate the Ephemeral ECDH performance based on these papers. While the ATmega4808 is capable of operating at a maximum frequency of 20 MHz, much of the ECDH research has focused on the 7.37 MHz of the ATmega128. For fairness, we benchmark Kyber at this same frequency. The state-of-the-art implementation in [61] focuses on the NIST Curve P-256, which provides a security level equivalent to Kyber-512. Our implementation of Kyber-512 reduces the key establishment time by roughly 1.5 seconds compared to [61]. More impressively, our Kyber-768 variant, despite its enhanced security, manages to achieve faster key establishment times than the state-of-the-art P-256-based ECDH implementation in [61]. For a comparison of energy consumption, see Appendix J.

Table 7: Average handshake times in second for mutually authenticated KEM-MQTT experiments (Excluding the physical transmission time during handshake). Also, We report the maximum memory peak during the handshake.

| KEM-MOTT     | Publisher sent req. |          | Publisher recv. resp. |          |

|--------------|---------------------|----------|-----------------------|----------|

| TEENI MIQI I | speed               | stack[B] | speed                 | stack[B] |

| Kyber-512    | 13,876k             | E 726    | 17,957k               | 5.184    |

| (★ ◊ †)      | 1.88s               | 5,726    | 2.44s                 | 3,104    |

$\star$ ,  $\diamond$ , and  $\dagger$ : same as Table 8

(based [16])

| T                         | Vaniant    |   | Kybe              | er-512   | Kybe              | er-768   | Kybe              | r-1024   |

|---------------------------|------------|---|-------------------|----------|-------------------|----------|-------------------|----------|

| Implementation            | Variant    |   | cc                | stack[B] | cc                | stack[B] | cc                | stack[B] |

| This Work<br>(Signed LUT) |            | K | 5,253k<br>(+82%)  | 3,720    | -                 | -        | -                 | -        |

|                           | * \ ‡      | E | 6,402k<br>(+101%) | 3,808    | 9,694k<br>(+101%) | 4,308    | 14,974k<br>(+99%) | 4,828    |

|                           |            | D | 6,706k<br>(+86%)  | 3,720    | -                 | -        | -                 | -        |

| This Work<br>(Signed LUT) | <b>*</b> † | K | 5,290k<br>(+81%)  | 2,220    | 8,608k<br>(+81%)  | 2,736    | 13,640k<br>(+80%) | 3,256    |

|                           |            | E | 7,385k<br>(+75%)  | 2,308    | 11,169k<br>(+75%) | 2,808    | 16,946k<br>(+76%) | 3,328    |

|                           |            | D | 6,763k<br>(+85%)  | 2,324    | 10,250k<br>(+85%) | 2,824    | 15,773k<br>(+80%) | 3,352    |

| This Work                 |            | K | 9,541k            | 2,220    | 15,554k           | 2,736    | 24,433k           | 3,256    |

| Inis work                 | *          | E | 12,879k           | 2,308    | 19,500k           | 2,808    | 29,347k           | 3,328    |

Table 8: Cycle counts (cc) and stack usage (bytes) for all security level of Kyber on 8-bit AVR MCUs. 1,000 cc is denoted by k.

18,796k

2,324

## 7.5 KEM-MQTT Communication Requirements

D

12,484k

To evaluate the handshake process, we simulate an MQTT publisher establishing a secure connection with a broker and transmitting an encrypted message. The experiment is conducted with a payload size of 256 bits, excluding the fixed and variable headers. The payload consists of a 64-bit timestamp (t), a 64-bit topic (T), and 128-bit data (d) (cf. Figure 4). Table 7 shows the actual time taken during the KEM-MQTT handshake process, excluding the physical transmission time. Although the ATmega4808 can operate at up to 20MHz, it runs at 7.37MHz to avoid confusion with Table 6. The measurement includes the time required for KEM (Kyber-512), key-schedule, AEAD, and packet generation. The key-schedule process is implemented identically to the key schedule in TLS 1.3, as described in Appendix C. As mentioned in section 6.5, we implement AEAD using handwritten assembly. When the publisher sends the initial message to the broker (Publisher sent req.), it takes approximately 1.88 seconds, and an additional 2.44 second before the broker receives the message and sends application data (Publisher recv. resp.). During the handshake, the maximum stack usage was measured at 5,726 bytes.

## 8 Conclusion and Future Work

The transition to Post-Quantum Cryptography (PQC) is gaining momentum today. Partially driven by concerns over "store now, decrypt later" attacks, the migration to PQC is already underway before fully fault tolerant quantum computers become widely available. Most research indicates that PQC is competitive with existing cryptography methods (e.g. ECDH and ECDSA) and can be implemented within certain constraints. However, many papers emphasize that transitioning to PQC is not just about replacing algorithms, and particularly with PQC-DSA, there can be costs in terms of increased memory consumption and latency. In embedded environment, research on PQC migration has primarily focused on

devices like Cortex-M4, where highly optimized PQC implementations exist. In contrast, migrating PQC to more constrained devices like 16-bit MSP430 and 8-bit AVR remains unclear.

28,377k

3,352

2,824

In this paper, we highlighted the lack of NIST PQC migration research on the 8-bit AVR platform over the past eight years and demonstrated that state-of-the-art implementation techniques are inefficient in AVR environments. Consequently, we pushed the performance of Kyber, a PQC standard, to its limits by introducing a novel modular multiplication method, achieving an efficient implementation on AVR with minimal stack usage. Additionally, we implemented a wireless sensor network communication protocol called KEM-MQTT. Drawing inspiration from the KEMTLS method, we enhanced the security of MQTT without using PQC-DSA. By successfully migrating PQC to the most resource-constrained devices, we have opened the door for future research into applying PQC to other protocols such as Bluetooth and Wi-Fi, as well as to other low-power devices beyond AVR. For example, 16-bit MSP430, with more available resources than AVR, may offer a more accessible path forward. Our work provides insights into the feasibility of PQC implementation in resource-constrained environments and paves the way for future studies aimed at enhancing security in embedded devices.

## Acknowledgments

The authors would like to thank the anonymous reviewers and the shepherd for their constructive feedback. This work was partly supported by the Institute of Information & Communications Technology Planning & Evaluation (IITP) grant funded by the Korea government (MSIT) (No. RS-2024-00444170, Research and international collaboration on trust model-based intelligent incident response technologies in 6G open network environment, 50%) and supported by the National Research Foundataion of Korea (NRF) grant funded by MSIT (No. 2022R1C1C1013368, 50%)

<sup>★:</sup> based on the stack optimize version of [16], ◊: pre-hased pk in flash memory, †: placing LUTs in flash memory, ‡: placing LUTs in stack

#### References

- Amin Abdulrahman, Jiun-Peng Chen, Yu-Jia Chen, Vincent Hwang, Matthias J Kannwischer, and Bo-Yin Yang. 2021. Multi-moduli NTTs for saber on Cortex-M3 and Cortex-M4. Cryptology ePrint Archive (2021).

- [2] Amin Abdulrahman, Vincent Hwang, Matthias J Kannwischer, and Amber Sprenkels. 2022. Faster kyber and dilithium on the cortex-M4. In Applied Cryptography and Network Security: 20th International Conference, ACNS 2022, Rome, Italy, June 20–23, 2022. Springer, 853–871.

- [3] YM Agus, Muhammad Ary Murti, Fery Kurniawan, Niken DW Cahyani, and Gandeva B Satrya. 2020. An efficient implementation of ntru encryption in postquantum internet of things. In 2020 27th International Conference on Telecommunications (ICT). IEEE, 1–5.

- [4] Erdem Alkim, Yusuf Alper Bilgin, Murat Cenk, and François Gérard. 2020. Cortex-M4 optimizations for {R, M} LWE schemes. IACR Transactions on Cryptographic Hardware and Embedded Systems (2020), 336–357.

- [5] Allied Market Research. [n.d.]. 8-Bit Microcontroller Market Size, Share, Competitive Landscape and Trend Analysis Report, by Type and, by Industry Vertical: Global Opportunity Analysis and Industry Forecast, 2023-2032. https://www.alliedmarketresearch.com/8-bit-microcontroller-market-A10035.

- [6] Derek Atkins. 2021. Requirements for post-quantum cryptography on embedded devices in the IoT. In *Third PQC Standardization Conference*.

- [7] Atmel. 2016. AVR Instruction Set Manual. https://www1.microchip.com/downloads/en/devicedoc/atmel-0856-avr-instruction-set-manual.pdf.

- [8] Roberto Avanzi, Joppe Bos, Léo Ducas, Eike Kiltz, Tancrède Lepoint, Vadim Lyubashevsky, John M. Schanck, Peter Schwabe, Gregor Seiler, and Damien Stehlé. 2020. CRYSTALS-Dilithium. Submission to the NIST Post-Quantum Cryptography Standardization Project [57]. https://pq-crystals.org/dilithium/.

- [9] Roberto Avanzi, Joppe Bos, Léo Ducas, Eike Kiltz, Tancrède Lepoint, Vadim Lyubashevsky, John M. Schanck, Peter Schwabe, Gregor Seiler, and Damien Stehlé. 2020. CRYSTALS-Kyber. Submission to the NIST Post-Quantum Cryptography Standardization Project [57]. https://pq-crystals.org/kyber/.

- [10] Seungyeon Bae, Yousung Chang, Hyeongjin Park, Minseo Kim, and Youngjoo Shin. 2022. A Performance Evaluation of IPsec with Post-Quantum Cryptography. In International Conference on Information Security and Cryptology. Springer, 249– 266.

- [11] Seungyeon Bae, Yousung Chang, Hyeongjin Park, Minseo Kim, and Youngjoo Shin. 2022. A performance evaluation of ipsec with post-quantum cryptography. In *International Conference on Information Security and Cryptology*. Springer, 249–266.

- [12] Brian Baldwin, Richard Moloney, Andrew Byrne, Gary McGuire, and William P Marnane. 2009. A hardware analysis of twisted Edwards curves for an elliptic curve cryptosystem. In *International Workshop on Applied Reconfigurable Computing*. Springer, 355–361.

- [13] Paul Barrett. 1986. Implementing the Rivest Shamir and Adleman public key encryption algorithm on a standard digital signal processor. In Advances in Cryptology—CRYPTO'86. Springer, 311–323.

- [14] Hanno Becker, Vincent Hwang, Matthias J Kannwischer, Bo-Yin Yang, and Shang-Yi Yang. 2021. Neon NTT: faster dilithium, Kyber, and saber on Cortex-A72 and Apple M1. Cryptology ePrint Archive (2021).

- [15] Joppe W. Bos, Joost Renes, and Amber Sprenkels. 2022. Dilithium for Memory Constrained Devices. Cryptology ePrint Archive, Paper 2022/323. https://doi. org/10.1007/978-3-031-17433-9\_10

- [16] Leon Botros, Matthias J Kannwischer, and Peter Schwabe. 2019. Memory-efficient high-speed implementation of Kyber on Cortex-M4. In Progress in Cryptology— AFRICACRYPT 2019: 11th International Conference on Cryptology in Africa, Rabat, Morocco, July 9–11, 2019, Proceedings 11. Springer, 209–228.

- [17] CHANDLER, Ariz. 2021. New 8-bit MCU Development Board Connects to 5G LTE-M Narrowband-IoT Networks. https://www.microchip.com/en-us/about/news-releases/products/new-8-bit-mcu-development-board-connects-to-5g-lte-m-narrowband.